# Incomplete Recovered Document with document format translation !! issues !!

# ImagiNE 2

The IMAGe engINE

Documentation & User Manual

May 1997

VERSION 0.70

| 4. THE REGISTER FILE                                                                                                                                        |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 4.1 introduction                                                                                                                                            |  |

| 4.1.1 the control registers                                                                                                                                 |  |

| 4.1.2 the vector index generators                                                                                                                           |  |

| 4.1.3 the access modes                                                                                                                                      |  |

| 4.2 The control registers                                                                                                                                   |  |

|                                                                                                                                                             |  |

| 4.2 Register plus register to register mode:                                                                                                                |  |

| <ul><li>4.2.1 accesses to general purpose and control registers</li><li>4.2.2 vector register accesses</li></ul>                                            |  |

| 4.2.3 The extended-indexed-accesses                                                                                                                         |  |

|                                                                                                                                                             |  |

| 4.3 Immediate plus register to register mode                                                                                                                |  |

| 4.4 The 16 bit constant load                                                                                                                                |  |

| 4.5 The 32 bit constant load / merge                                                                                                                        |  |

| 4.6 Vector index generators                                                                                                                                 |  |

| 4.6.1 results of the index generators                                                                                                                       |  |

| 4.6.2 control input for the Index generators                                                                                                                |  |

| 4.6.3 data input for the Index generators                                                                                                                   |  |

| 4.6.4 Index generator calculations                                                                                                                          |  |

| 4.6.5 select the data bus used for the offset data                                                                                                          |  |

| 4.6.6 select the status for conditional index generation and byte write enables                                                                             |  |

| 4.6.7 select between the use of the current or delayed status                                                                                               |  |

| 4.6.8 generation of the byte write enables                                                                                                                  |  |

| 4.6.9 generation of the byte presets and byte resets                                                                                                        |  |

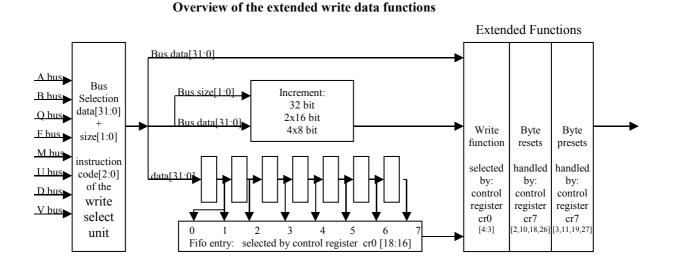

| 4.7 The extended functions                                                                                                                                  |  |

| 4.7.1 byte write enables                                                                                                                                    |  |

| 4.7.2 On the fly write Functions                                                                                                                            |  |

| 4.7.3 application of the byte presets and byte resets                                                                                                       |  |

| 4.7.4 run time programmable data sizes                                                                                                                      |  |

| 4.7.5 preserved for compatibility only                                                                                                                      |  |

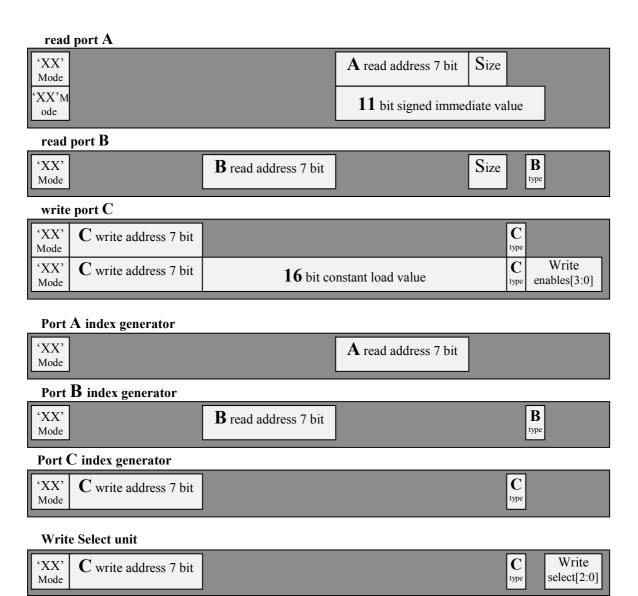

| 4.8 The 7 independent sub units of the register file                                                                                                        |  |

| 4.8.1 read port A span of control                                                                                                                           |  |

| 4.8.2 read port B span of control                                                                                                                           |  |

| 4.8.3 write port C span of control                                                                                                                          |  |

| 4.8.4 read port A index generator span of control                                                                                                           |  |

| 4.8.5 read port B index generator span of control                                                                                                           |  |

| <ul><li>4.8.6 write port C index generator span of control</li><li>4.8.7 write Select Unit span of control</li></ul>                                        |  |

| -                                                                                                                                                           |  |

| <b>4.9</b> Instruction fields for each of the 7 sub-units of the register file                                                                              |  |

| 4.9.1 default values of instruction code fields                                                                                                             |  |

| 4.10 Events which modify the Register File's control registers                                                                                              |  |

| 4.10.1 events which modify REG_Control                                                                                                                      |  |

| 4.10.2 events which modify REG_Monitor                                                                                                                      |  |

| 4.10.3 events which modify REG_Vector                                                                                                                       |  |

| <ul><li>4.10.4 events which modify REG_A_Indices.</li><li>4.10.5 events which modify REG_B_Indices.</li></ul>                                               |  |

| 4.10.5 events which modify REG_D_Indices                                                                                                                    |  |

| 4.10.0 events which modify REG_C_flags                                                                                                                      |  |

|                                                                                                                                                             |  |

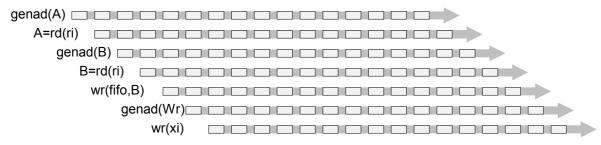

| 4.11 Examples of vector operations with the register file                                                                                                   |  |

| 4.11.1 Example 1: Vectored 3 operand ROP with an 8x8 pattern                                                                                                |  |

| 4.11.2 Example 2: Vectored parallel min/ max function                                                                                                       |  |

| 4.11.3 Example 3: Vectored parallel table look up function                                                                                                  |  |

| <ul><li>4.11.4 Example 4: Vectored parallel histogram function</li><li>4.11.5 Example 5: Vectored parallel add / subtract with saturate functions</li></ul> |  |

| 4.11.5 Example 5: Vectored parallel run length encoder                                                                                                      |  |

| T.II.O Example 0. Youthou parametrum tengui cheouch                                                                                                         |  |

| 4.12 Interrupt processing:                                                                                                              | 44 |

|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| 5. BARREL SHIFT/ROTATE UNIT                                                                                                             |    |

| 5.1 operations                                                                                                                          |    |

| 5.1.1 Operand select                                                                                                                    |    |

| 5.1.2 Barrel shift functions                                                                                                            |    |

| 5.1.3 Shift direction                                                                                                                   |    |

| 5.1.4 The result register of the Barrel Shifter                                                                                         |    |

| 5.1.4 The extended function of the Barrel Shifter                                                                                       |    |

| 6. ARITHMETIC & LOGIC UNIT                                                                                                              | 49 |

| 6.1 Operand Source select:                                                                                                              |    |

| 6.2 ALU function:                                                                                                                       |    |

| 6.3 ALU instruction set                                                                                                                 |    |

| 6.4 Three port parametrised logic functions                                                                                             |    |

| 6.5 ALU control register: logic_function                                                                                                |    |

| 6.6 The ALU status register                                                                                                             |    |

| 6.7 Conditional Control Flow Processing:                                                                                                |    |

| 6.8 using status for conditional register access                                                                                        |    |

| 6.9 using status for the range mask:                                                                                                    |    |

| 6.10 direct control register access to the F bus register:                                                                              | 53 |

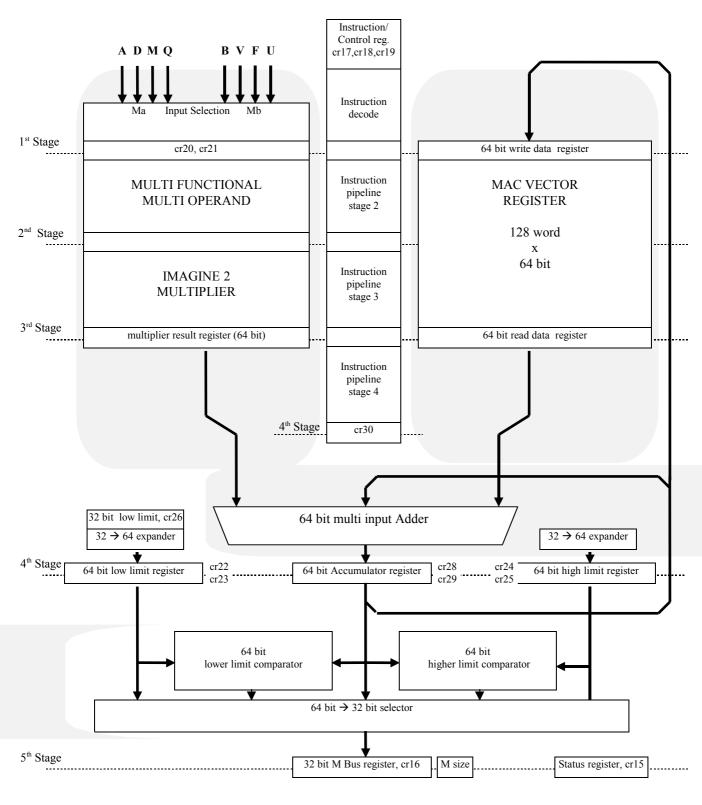

| 7. MULTIPLIER / ACCUMULATOR                                                                                                             |    |

| 7.1 Multiplier / Accumulator                                                                                                            |    |

| 7.1.1 The multiplier accumulator                                                                                                        |    |

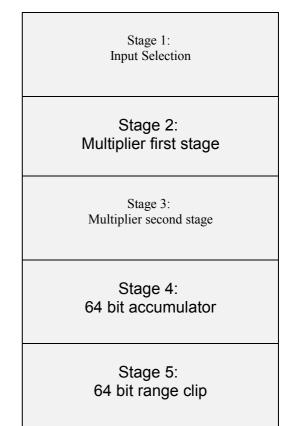

| 7.1.2 The pipeline                                                                                                                      |    |

| 7.1.3 multiplier operand select                                                                                                         |    |

| 7.2 The basic set of multiplier operations                                                                                              |    |

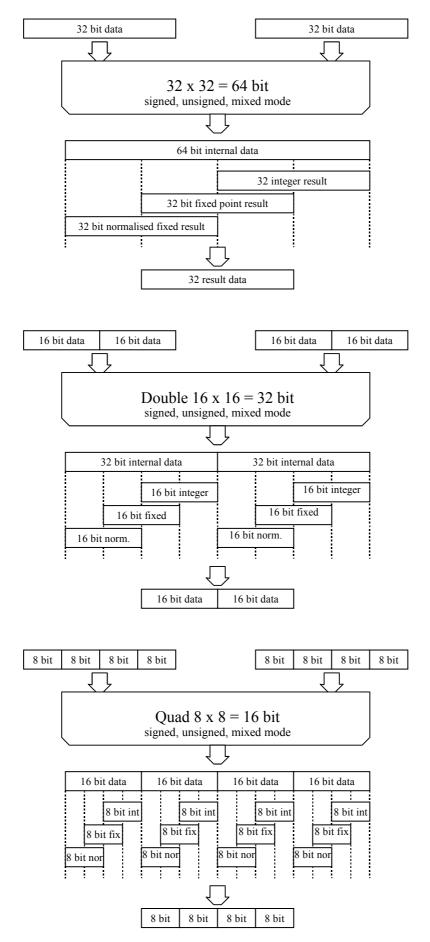

| 7.2.1 The Basic Multiply options                                                                                                        |    |

| 7.2.2 Multiplications defined in the basic set                                                                                          |    |

| 7.2.3 The multiplier operand types                                                                                                      |    |

| 7.2.4 Internal and output formats                                                                                                       |    |

| 7.2.5 The Graphics data format                                                                                                          |    |

| 7.3 The extended multiplier functions                                                                                                   |    |

| 7.4 Description of the multiplier operations                                                                                            |    |

| 7.4.1 Operands for the multiplier                                                                                                       |    |

| 7.4.2 Basic operations.                                                                                                                 |    |

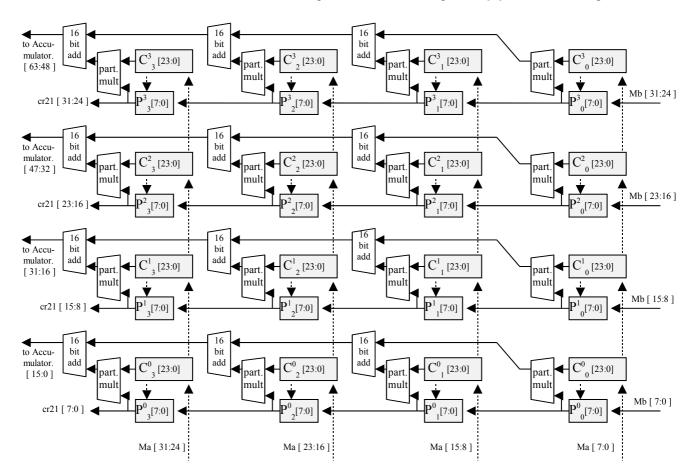

| <ul><li>7.4.3 8 bit Matrix functions: Quad Inproduct</li><li>7.4.4 8 bit Matrix functions: 8 bit Matrix Vector multiplication</li></ul> |    |

| 7.4.5 8 bit Matrix functions: 8 bit Matrix vector multiplication                                                                        |    |

| 7.4.6 Data Pipeline initialisation:                                                                                                     |    |

| 7.4.7 Accumulator file access                                                                                                           |    |

| 7.4.8 Reading data from the accumulator file                                                                                            |    |

| 7.4.9 Writing data to the accumulator file                                                                                              |    |

| 7.4.10 Incremental Functions                                                                                                            |    |

| 7.4.11 The MAC functions: multiply accumulate (scalar)                                                                                  |    |

| 7.4.12 The MAC functions: multiply accumulate (block)                                                                                   |    |

| 7.4.13 16 bit vector product                                                                                                            |    |

| 7.4.14 16 bit complex product                                                                                                           |    |

| 7.5 Multiplier / accumulator operand formats                                                                                            |    |

| <ul><li>7.5.1 Multiplier input and output format definitions.</li><li>7.5.2 Internal format definitions.</li></ul>                      |    |

|                                                                                                                                         |    |

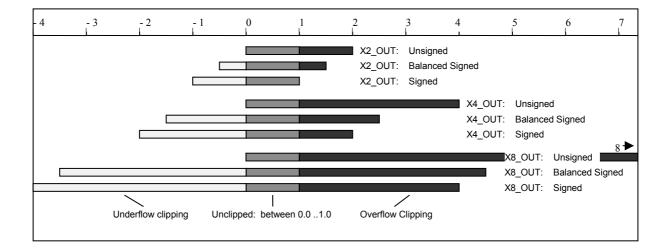

| <b>7.6</b> The range clip unit                                                                                                          |    |

| 7.6.2 Range clip activation.                                                                                                            |    |

| 7.6.3 Data size and data Type                                                                                                           |    |

| 7.6.4 Range clip output                                                                                                                 |    |

| 7.6.5 The status word: ALU_RC_Status (=cr15)                                                                                            |    |

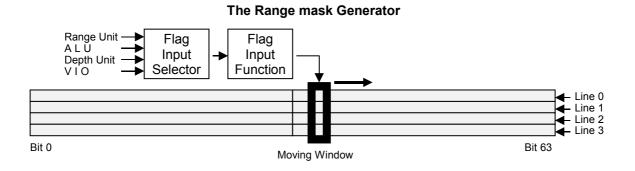

| 7.6.6 The range mask generator                                                                                                          |    |

| 7.6.7 Balanced signed compares                                                                                              | 66                                      |

|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| 7.7 Overview of the multiplier control registers                                                                            | 67                                      |

| 7.8 Multiplier accumulator control register 1                                                                               | 68                                      |

| 7.8.1 The vector ram read / write control                                                                                   |                                         |

| 7.8.2 The operand Data Size field                                                                                           |                                         |

| 7.8.3 The Data Type control field                                                                                           |                                         |

| 7.8.4 The Accumulator input selection                                                                                       |                                         |

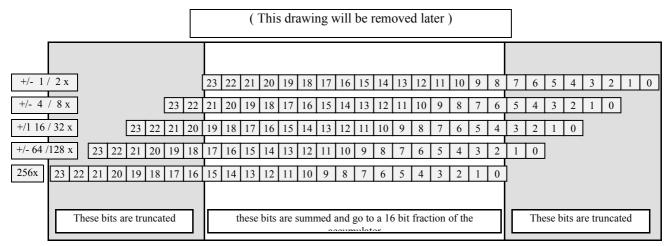

| 7.8.5 Output shift factor                                                                                                   |                                         |

| 7.8.6 The Range clip unit activation flag                                                                                   |                                         |

| 7.8.7 The pipeline control field                                                                                            |                                         |

| 7.8.8 Transposer operation                                                                                                  |                                         |

| 7.9 Multiplier accumulator control register 2                                                                               | 70                                      |

| 7.9.1 blend coefficient selection                                                                                           |                                         |

| 7.9.2 range unit: 32 or 64 bit compares                                                                                     |                                         |

| 7.9.3 range unit:                                                                                                           |                                         |

| Balanced signed compare:                                                                                                    |                                         |

| 7.9.4 range unit:                                                                                                           |                                         |

| Dynamic Limits                                                                                                              |                                         |

| 7.9.5 range unit:                                                                                                           |                                         |

| Range Mask selection                                                                                                        |                                         |

| 7.9.6 range unit:                                                                                                           |                                         |

| Output clipping                                                                                                             | 71                                      |

| 7.10 Multiplier accumulator pointer control register                                                                        |                                         |

| 7.10.1 Vector register ram read and write pointers                                                                          |                                         |

| 7.10.2 Coefficient read and write pointers.                                                                                 |                                         |

| 7.10.3 The data type and signs used for macs()                                                                              | 72                                      |

|                                                                                                                             | 73                                      |

| 7.11 Multiplier accumulator coefficient register entry                                                                      | ······//                                |

| 7.11 Multiplier accumulator coefficient register entry                                                                      |                                         |

| 7.12 Multiplier accumulator 8 bit data pipeline output                                                                      | 73                                      |

| <ul><li>7.12 Multiplier accumulator 8 bit data pipeline output</li><li>7.13 The state save and restore register</li></ul>   |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li> <li>7.13 The state save and restore register</li></ul> | 73<br>                                  |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li> <li>7.13 The state save and restore register</li></ul> | 73<br>73<br>74<br>76                    |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li> <li>7.13 The state save and restore register</li></ul> |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li> <li>7.13 The state save and restore register</li></ul> |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li> <li>7.13 The state save and restore register</li></ul> |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li> <li>7.13 The state save and restore register</li></ul> |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li> <li>7.13 The state save and restore register</li></ul> |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li> <li>7.13 The state save and restore register</li></ul> |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li> <li>7.13 The state save and restore register</li></ul> |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li> <li>7.13 The state save and restore register</li></ul> |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li> <li>7.13 The state save and restore register</li></ul> |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li> <li>7.13 The state save and restore register</li></ul> |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li> <li>7.13 The state save and restore register</li></ul> |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li></ul>                                                   |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li></ul>                                                   |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li></ul>                                                   |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li></ul>                                                   |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li></ul>                                                   |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li></ul>                                                   |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li></ul>                                                   | <b>73 74 74 76 76 76 76 76 77 77 77</b> |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li></ul>                                                   | <b>73 74 74 76 76 76 76 76 77 77 77</b> |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li></ul>                                                   | <b></b>                                 |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li></ul>                                                   | <b>73 74 74 76 76 76 76 77 77 77 77</b> |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li></ul>                                                   |                                         |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li></ul>                                                   | <b>73 74 74 76 76 76 76 76 76 77 77</b> |

| <ul> <li>7.12 Multiplier accumulator 8 bit data pipeline output</li></ul>                                                   | <b>73 74 74 76 76 76 76 76 76 77 77</b> |

| 0.4.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | UNF: Underflow error flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ) OVF: Overflow error flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ERR: Floating point error flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | EEE-754 floating point conversions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                      |

| 8.5.1<br>8.5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | The pass instruction<br>The IEEE 754 conversion instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IEEE 32 bit floating point to integer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | IEEE 52 on nouting point to integer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 32 bit floating point to fixed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Integer to IEEE 32 bit floating point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Fixed to IEEE 32 bit floating point                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                      |

| 8.5.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Some examples of floating point to integer conversions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 82                                                                                                                                                                   |