# ELEKTRONICA

VAKBLAD VOOR ELEKTRONICUS EN INFORMATICUS

- Regionale test- en meetdagen van Het Instrument

- Centrum voor Micro-Elektronica op één adres

- Imagine voegt zich naar programma en applicatie

## ELEKTRONICA

#### 15 april 1994, 42e jaargang

Uitgave: Kluwer Techniek postbus 23, 7400 GA Deventer Tel: (05700) 48700 fax: (05700) 42761

Kluwer Techniek is een onderdeel van Kluwer BedrijfsInformatie BV

verschijnt 19 X per jaar.

#### Redactie:

fax: (05700) 10918 Hoofdredact ing. H.H.W.M. de Vries Eindredactie: E.Th. van Gelder (05700) 48699 J.C. Meijer (05700) 48702 Nieuwsredactie: B.M. Kaauw (05700) 48695

#### Uitgever:

R.J. van Berkel Lezersmarkt: P. Rekveld Hoofd advertentie-exploitatie:

#### H. Meijerink Medewerkers:

ing. J. Bremer, P. de Casparis, E. Fuchs, ir. J.P.C. van Gennip, ir. G. Huisman, dr. M.T.H.C.W. Huisman-Stam, ir. F.H.J.F. Janssen, ir. L.P. de Jong, G. Kooren, J. Kosterman, H. Leydens, ing. Th.C. Lof, J.W. van Nigtevegt, dr.ir. E.H. Nordholt, W.J.M. Lemmens, ing. Th.W. Polet, ir. G.A. van der Pijll, D.J.W. Sjobbema, J.G. Smilde, A.S. Sterrenburg, ing. J. Stevens, ir. J.M. van Thiel, ing. A.H. Verbunt, drs. H.W. de Waard, A. Weigand, R. van der Zwan

#### Correspondenten:

Atlantic News Association (VS), dr. W. Baier (Duitsland)

M. Flameling (05700) 48743, M. de Boer (05700) 48718. fax: (05700) 19904

Advertentie-opdrachten worden uitgevoerd overeenkomstig onze everingsvoorwaarden gedeponeerd ter Griffie van de Arrondissementsrechtbanken en de Kamers van Koophandel

#### Abonnementen en losse nummers Abonnementenregistratie: mevr. S. Broekhof

Jaarabonnement: Nederland f 169,50 (incl. BTW) België: BF 3320 Buitenland f 313 Losse nummers: Nederland f 11,25 (incl. BTW) België: BF 250 Studentenkorting: 40% Elektronica is uitsluitend op abonnementsbasis verkrijgbaar. Een abonnement kan elk gewenst moment ingaan osse nummers + opgave abonnementen (05700) 48607

Betalingen + adreswijzigingen (05700) 48607

#### Betaling:

Nieuwe abonnees ontvangen een stortings-acceptgirokaart.

#### Opzegging abonnementen:

Beëindiging abonnement kan uitsluitend schriftelijk geschieden, uiterlijk twee maanden voor het einde van uw abonnementsperiode, nadien vindt automatisch verlenging plaats.

Het auteursrecht t.a.v. de redactionele inhoud van dit tiidschrift w Ongeautoriseerde verveelvuldiging enfof openbaarmaking van het geheel of gedeelten daarvan op welke wijze ook is verboden" 1994.

Het verlenen van toestemming tot publikatie in dit tijdschrift houdt in dat de auteur de "met vereinen van toessemining tot publikate in dit tijdschrift houdt in ast die auteur de uitgever, met uitgalien van inder ander, onhervongelijk machtigt die bijd if krachtens die Auteurswert door derden verschuldigde vergoeding voor kopiëren te innen of daarnoe in en buiten rechte op te treden en dat die auteur er mee instem dat die uitgever deze vollmacht overdraagt aan die door auseurs en uitgeversrengen voordigers bestuurde Schotting Reprotecht – tot welke overdracht die uitgever zich zijnetzijds verbindt – en dat deze Schotting an die te innen gelden een in overeenstemming met haar statuten en regiementen bepaalde bestemming geeft".

lid NOTU, Nederlandse Organisatie van Tijdschrift-Uitgevers; lid FPPB, Federatie van de Periodieke Pers van België ISSN 0168-7840.

Koggeschip Offset BV, Amsterdam.

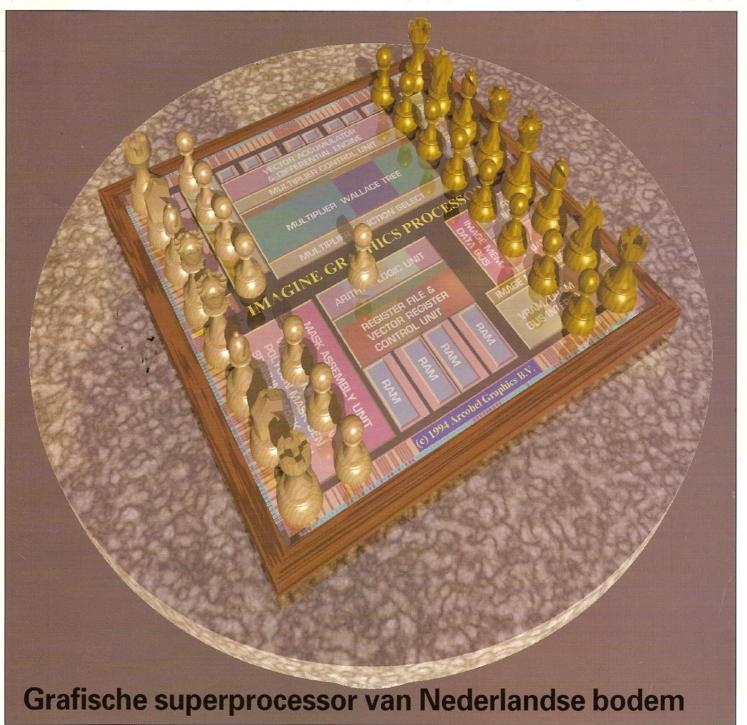

'Imagine' heet de grafische processor die Arcobel Graphics heeft ontwikkeld. In een evolutieproces dat enkele jaren heeft geduurd en dat begon bij de eveneens op grafische verwerking gerichte dataflow-computer van het ter ziele gegane Dataflow Technology Nederland, ontstond een chip met een aantal opvallende kenmerken. Zo kunnen alle interne eenheden parallel werken, in een gegevenspijplijn die geheel softwarematig kan worden bepaald. Bovendien levert het werken met kleinere woordbreedten, 8 of 16 bit in plaats van 32 bit, nog eens een lineaire of zelfs - in het geval van de vermenigvuldiger kwadratische snelheidswinst op. In pieken levert dat een verwerkingscapaciteit van 8000 Mips op, voldoende om de huidige Risc-processoren er in grafische applicaties met een factor vijf tot twintig uit te lopen. (Illustratie: Arcobel Graphics)

#### ACTUEEL

| Elektronicamarkt | 8  |

|------------------|----|

| Pen 16           | 9  |

| Journaal         | 10 |

| Verhuizingen     | 10 |

| Agenda           | 11 |

| Zakennieuws      | 12 |

| Personalia       | 12 |

|                  |    |

#### METEN

### Regionale test- en meetdagen

De Nederlandse branchevereniging voor Industriële Elektronica van Het Instrument organiseert op 19, 20 en 21 april drie regionale 'T&M-dagen'. Zestien lidbedrijven uit de groep 'elektronica meetinstrumentatie' presenteren in achtereenvolgens Eindhoven, Leiden en Zwolle hun testen meetprodukten en technieken. Elke dag is er een kleine produktenshow en vinden er veertien korte presentaties plaats. ELEKTRONICA geeft een overzicht van het programma en een korte samenvatting van een aantal van de lezingen. 14

#### **ADVIES**

#### Kennis stroomt niet vanzelf

Het Centrum voor Micro-Elektronica heeft een nieuw adres. Eén adres. Voorheen was het CME te vinden in drie prominente plaatsen, Delft, Eindhoven en Enschede, steeds in de luwte van een technische universiteit. Nu is er alleen het verlegen Veenendaal... heel centraal, helemaal op zichzelf. Algemeen directeur ir. B. Krijgsman en directeur externe betrekkingen ir. H.J. Bosch hebben er wel het een en ander over te melden.

#### CHIPBESPREKING

#### Imagine voegt zich naar programma en applicatie

Als je als klein bedrijf een processor ontwerpt die internationaal in de voorste gelederen mee moet kunnen draaien, is kostenbesparing de enige mogelijkheid om reuzen als DEC, HP en Intel bij te

blijven. Bij de Imagine hebben in dat opzicht de software- en hardwaremodellen centraal gestaan, die er samen toe moeten leiden dat in één keer werkend silicium wordt verkregen.

#### Grafische superprocessor 'hergebruikt' transistoren

Professionele DTP, real-time video, CAD/CAM, simulatoren, kleurenlaserprinters en soortgelijke zware grafische applicaties, dat zijn de toepassingen waarvoor de Imagine zich het beste leent. De tot op zeer laag niveau programmeerbare processor heeft voor optimale prestaties wel uitgekiende opcodes nodig. Vandaar dat wordt gewerkt met een hiërarchische instructieset.

48 **PRODUKTEN**

Het volgende nummer van Elektronica verschijnt op 29 april

Innovatief chipconcept vermindert transistorwerkloosheid

# Imagine voegt zich naar programma en applicatie

Op Nederlandse bodem wordt momenteel gewerkt aan de ontwikkeling van een grafische processor volgens een innovatief concept. Flexibele benutting van de hardware, daar draait het om en dit moet ertoe leiden dat de chip alle soortgenoten het nakijken gaat geven. Imagine is de naam die de ontwerpers van Arcobel Graphics aan hun CPU hebben gegeven. Het IC is nog niet op de markt, dat gaat binnenkort gebeuren, maar de specificaties beloven heel wat. De processor moet - vooral bij grafische applicaties vijf tot twintig keer meer presteren dan de snelste verwerkingseenheden van dit moment, waaronder de Pentium. Ook de 200-MHz Alpha heeft, ondanks de drie maal hogere klokfrequentie, bij derlijke toepassingen het nakijken. Het geheim zit 'm in de efficiente, variabele benutting van de hardware, wat het geheel meer maakt dan een conventionele Risc-CPU. Arcobel spreekt zelf van een 'algemeen toepasbare'-chip die vooral geschikt is voor beeldbewerking en grafisch werk: van DTP en 'Virtual Reality' tot real-time video. Resteert de vraag: hoe is dit alles mogelijk?

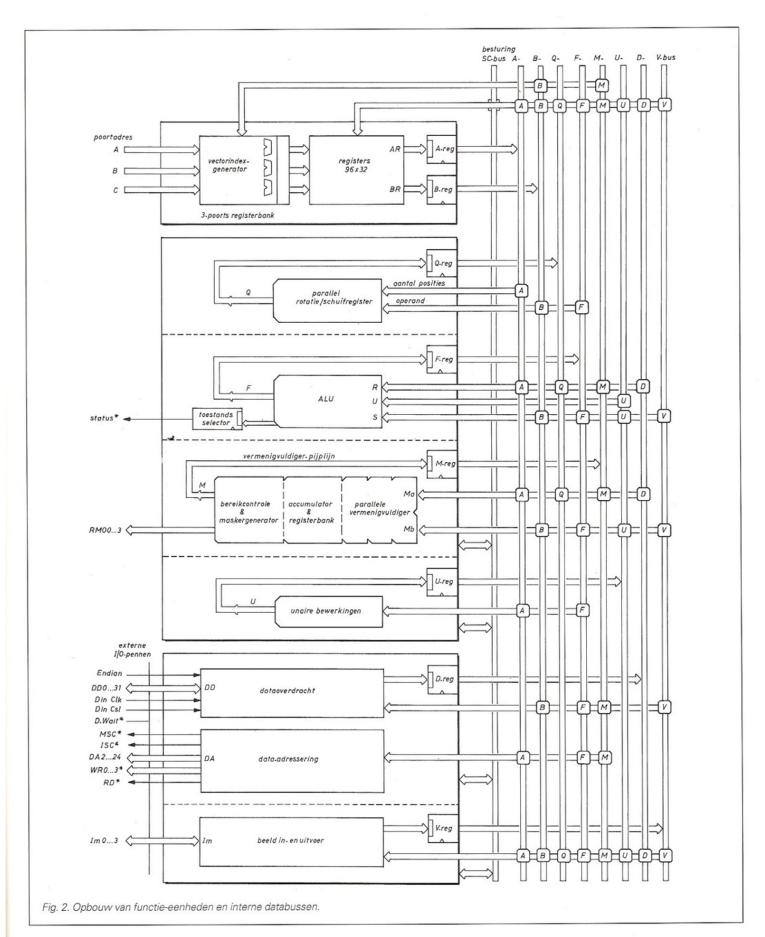

De meeste functie-eenheden in de Imagine beschikken over eigen datakanalen waardoor ze volledig parallel kunnen werken.

Arcobel Graphics kwam uiteindelijk op de naam Imagine als samentrekking van 'Image' en 'Engine'. Dat in die samentrekking ook een belofte verborgen zit ('Stel je toch voor...'), is een extra overweging geweest om voor deze naam te kiezen. Daarmee wordt impliciet duidelijk dat het Brabantse bedrijf de belofte niet schuwt. Wat op de grafische markt komt, moet pure potentie inhouden anders heeft het niet gek veel zin de hevige concurrentiestrijd aan te gaan.

'Belofte' is in de ogen van de makers niet zozeer een 50-MHz of 67-MHz processor op een enkele chip. De klokfrequenties van de twee uitvoeringen zijn weliswaar bepaald niet laag maar zeker niet spectaculair. Het bedrijf wijst liever op andere cijfers. Voor de 50-MHz versie zijn dat bijvoorbeeld een verwerkingssnelheid van 250 Mips met 32 bit-instructies. En wordt teruggeschakeld naar 8-bit operaties dan nemen, en daar zit het grote verschil met de soortgenoten, de prestaties nog sterk toe en is een piek van 6 000 Mips haalbaar.

#### Vergelijking

De cijfers krijgen iets meer zeggingskracht als die van de concurrentie ernaast worden gezet. Een gebruiker van het experimentele uur nam de gelegenheid te baat om de D

Per transistor gezien zijn de 8080 en zijn tijdgenoten vijftig tot honderd maal efficiënter dan huidige snelheidsmonsters als de Pentium.

> prestaties te vergelijken met die van een 200-MHz DEC Alpha. Het roteren van DTPbeelden met 32-bit kleurwaarden verliep bij de Alpha met 0,6 megapixels per seconde. De topuitvoering van de Imagine liet hier 6,7 Mpixels/s noteren. Bij medische toepassingen, die 8-bit grijsniveaus hanteren, waren die uitkomsten respectievelijk 2,9 en 33 Mpixels/s.

Dit zijn cijfers die – het valt niet te ontkennen – inderdaad van een belofte getuigen. Dat geldt niet in de laatste plaats voor de PC-gebruiker die straks gewoon een kaart met een Imagine in zijn computer kan steken om volop in de professionele grafische wereld en die van beeldverwerking mee te doen. Zo'n uitbreidingsmodule maakt het mogelijk om grafische bewerkingen 75 keer sneller uit te voeren dan met een gebruikelijke PC-configuratie van dit moment.

#### Naïef

Hoe kunnen de opvallende prestaties worden verklaard? Deze vraag laat zich volgens Arcobel anders stellen: is het mogelijk om op basis van de bestaande technologie de hardware zo te configureren dat dergelijke significante snelheidswinsten haalbaar zijn? Bij beantwoording van deze

retorische vraag acht het bedrijf een winst mogelijk van voorbij de duizend procent op basis van een nauwelijks gewijzigd aantal transistoren. Maar dan moet je niet beginnen met een technisch verhaal, stellen manager business development Sjef ten Den en ontwerper Hans de Vries met zoveel woorden. Begin eerst met de filosofie.

Dat filosofische verhaal vindt zijn oorsprong in – andermaal – koele cijfers. Het rendement van Cisc is de laatste vijftien jaar met een factor tien afgenomen, betogen ze in Den Bosch. Om dat aannemelijk te maken, presenteert het bedrijf een rekensommetje dat nog verder teruggaat in de tijd. In 1974 introduceerde Intel de 8080, die zo'n 5 000 transistoren telde.

Bijna twintig jaar later heeft het jongste familielid in de 80x8x-familie, de Pentium, ruim drie miljoen schakeleenheden, zeshonderd maal meer. Deze verveelvoudiging mag tot de verbeelding spreken maar vormt eigenlijk nog maar de helft van het verhaal: sinds 1974 bleef immers ook de klokfrequentie niet onberoerd. Ruwweg genomen valt te verdedigen dat die sinds 1974 is toegenomen met een factor 33.

De "ietwat naïeve gedachte" – de woorden zijn van Ten Den zelf – is dan dat de huidige processoren dus ongeveer 20 000

maal (= 600 x 33) zo snel moeten zijn. Elke elektronicus weet dat dit getal ver van de werkelijkheid staat. De snelheidswinst ligt rond een factor van enkele honderden, zeker niet van enkele duizenden, laat staan van 20 000.

#### Werkloze transistoren

Deze door de ontwerpers geopperde 'naïeve' aanname heeft iets buitengewoon aantrekkelijks. Tegelijk heeft de gedachtengang iets vertrouwds want de door de jaren heen gegroeide discrepantie tussen prestatie en potentie is aan anderen evenmin onopgemerkt voorbijgegaan. In feite is de Reduced Instruction Set Computer (Risc) het antwoord op de kennelijk niet optimale benutting van de netjes gespreide transistortuinen op een Cisc (Complex Instruction Set Computer). Wie het aantal instructies reduceert, heeft minder klokcyclussen voor een bewerking nodig.

Helemaal mooi is een applicatiespecifieke processor die slechts één taak hoeft uit te voeren. Variaties in de instructieset blijven uit; het hardware-rendement tendeert naar 100 procent. De prijs van zo'n geringe(re) instructieset is echter een beperkter toepassingsgebied.

Tot zover is er niets nieuws onder de zon. Toch wordt ook hier andermaal op onbevangen wijze een duidelijk gegeven weggewerkt. Wie een applicatiespecifieke CPU tegenover een Cisc-processor zet, merkt dat een specifieke verwerkingseenheid al gauw 25 maal zo snel en soms zelfs 100 keer zo snel zijn werk aflevert. Daaruit trekken Ten Den en De Vries opzettelijk de opzichtige – zij het wat eenvoudige – conclusie dat transistoren in een Cisc-architectuur maar 1 tot 4 procent van de tijd aan het werk zijn. Om het nog sterker uit te drukken: 99 tot 96 procent van de tijd is een transistor werkloos.

Mensen als Ten Den en De Vries hebben nadrukkelijk stil willen staan bij deze potentiële snelheidswinst. Feitelijk ging het om de vraag: kun je die hardwarepotentie benutten zonder te vervallen in de beperkte functionaliteit die Risc – laat staan een specifieke chip – nu eenmaal heeft? Complexiteit, lees: brede toepasbaarheid, moest samen kunnen gaan met snelheid. Het Engelse 'the best of both worlds' vertaalde zich in het Nederlandse 'het onderste uit de kan'.

#### Meerdere fronten

Wat inderdaad opvalt aan het ontwerp van de Imagine is dat op meerdere fronten 'strijd' is geleverd om de verwerkingssnelheid op niveau te brengen. Het ontwerpteam heeft zich niet tevreden gesteld met enkele architectonische wijzigingen, het is een combinatie van in elkaar passende

Hans de Vries (I) en Sjef ten Den: "het kost een maand of twee inwerken maar dan halen programmeurs een snelheidswinst van 1000%."

maatregelen. Dat blijken geen halve ingrepen te zijn: hier en daar is behoorlijk afgeweken van conventionele architecturen.

Desondanks is het uitgangspunt conventioneel: Risc. Dat de chip met, behulp van zijn C-compiler ook als een hormale CPU valt te programmeren, noemt De Vries erg belangrijk. "Elke nieuwe processor, dus ook de onze, moet in ieder geval gebruik kunnen maken van de Gigabytes aan software die al in deze taal geschreven is." De Vries doelt hierbij op de voornaamste applicaties: grafische taken en beeldverwerking. De eigenzinnige invulling die hij en zijn collega's aan de Risc-filosofie geven, heeft voor een zeer belangrijk deel te maken met dit applicatiegebied.

#### Open doel

Bij grafische toepassingen staat de opbouw van beelden centraal. Deze worden gerepresenteerd als tweedimensionale reeksen van 8-bit of 16-bit beeldpunten. Drie 8-bit bytes vormen samen een kleurenpixel, voor rood/groen/blauw-weergave terwijl bij DTP-toepassingen de beelden zijn opgebouwd uit 4x8 = 32 bit voor de 'drukkerskleuren' CMYK (cyaan/magenta/geel/zwart).

Drukkers streven naar zo'n half miljoen beeldpunten per vierkante centimeter terwijl real-time video in digitale vorm een datastroom van 30 Mbyte/s oplevert. Het belang van een snelle 8-bit en 16-bit verwerking is bij grafische toepassingen dus erg groot.

Schakeringsbewerkingen lenen zich uitstekend voor benutting van de interne parallelliteit.

De eenheden van een 32-bit Risc-processor voeren 8-bit bewerkingen echter niet sneller uit dan 32-bit operaties. Wel blijft in het eerste geval een flink deel van de hardware onbenut. Die conclusie levert weliswaar een schot voor open doel op maar tegelijk bleek het tot nu toe niet mogelijk goed te mikken: niemand slaagde erin dit euvel efficiënt te verhelpen.

#### Herschikking

De oplossing werd gevonden in herschikking van de transistoren en in toegevoegde controlelogica. De finesses laat ontwerper De Vries voor wat ze zijn. Maar feit is dat de Imagine op deze manier in dezelfde cyclus vier 8-bit bewerkingen (of twee 16-bit bewerkingen) kan uitvoeren waar anders maar één 8-bit bewerking op een 32-bit processor mogelijk zou zijn. Dit levert een lineaire winst op in bijvoorbeeld een ALU of schuifregister.

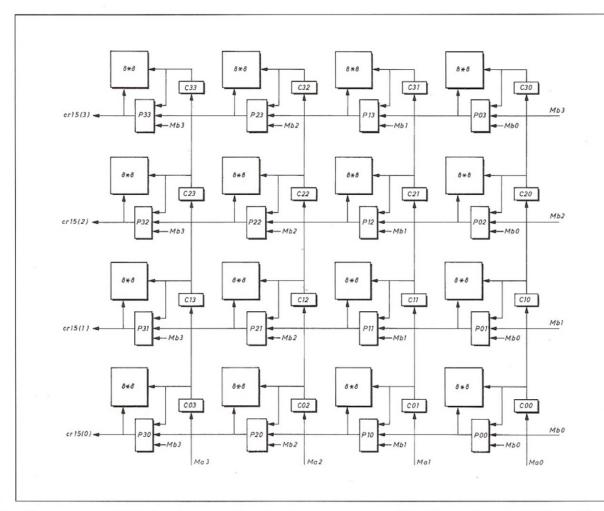

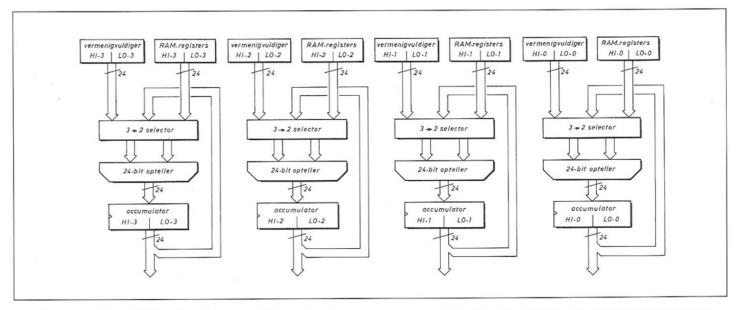

Binnen een andere functionele eenheid, de vermenigvuldiger, ligt de winst nog op een veel hoger niveau. Een 32-bit vermenigvuldiger vereist zestien maal zoveel transistoren als een soortgenoot van 8 bit. Zodoende is bij een parallelle verwerking van vier 8-bit vermenigvuldigingen de bezettingsgraad slechts 25 procent. Bovendien maken, zo rekent De Vries voor: "de mathematische mogelijkheden binnen de interne hardware van de vermenigvuldiger ook nog eens twaalf 8-bit optellingen mogelijk tijdens dezelfde klokcyclus. Zodoende levert een klokslag niet één, maar 28 bewerkingen op."

Door deze constructie kost een eenvoudige bewerking als het optellen van twee RGB-of CMYK-pixels (respectievelijk 3x8 en 4x8 bit) nog maar één ALU-klokslag in plaats van drie of vier. De Vries stelt volledigheidshalve dat de "mathematische mogelijkheden" in de vermenigvuldiger zeker geen academische exercities zijn. Alle mogelijkheden staan een programmeur concreet ter beschikking en zijn geschikt voor directe vertaling in belangrijke grafische basistaken zoals kleurenconversie en rotatie.

#### Onafhankeliik

Het eigenzinnige karakter van de Imagine houdt niet op bij het principe van gelijktijdige instructieacceptatie. Een inleidend betoog over de chip stelt dat 'het denken in

subeenheden' belangrijk is om de bestaande hardware zo doelmatig mogelijk te benutten. In zekere zin eindigt die verdeling pas op transistorniveau, zoals uit het voorbeeld van de gelijktijdige instructieacceptatie blijkt.

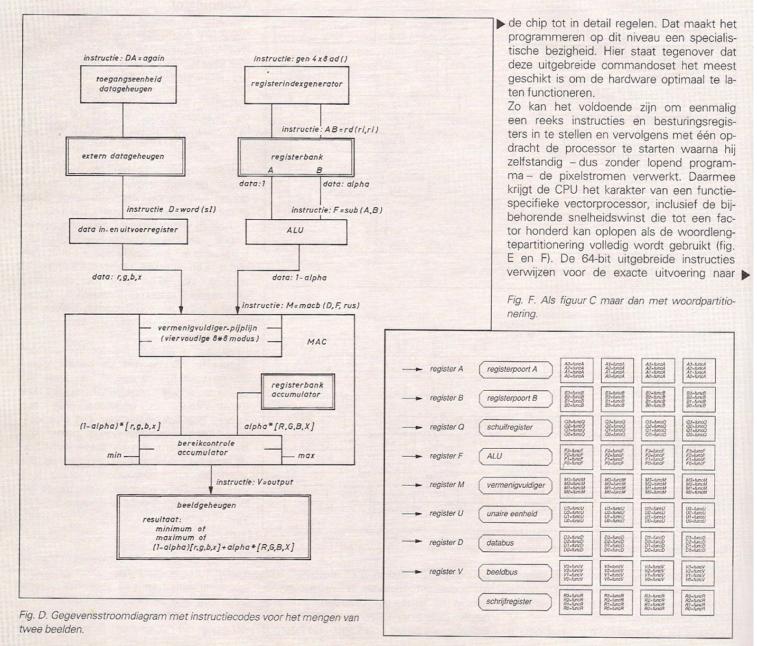

Op een wat hoger niveau, die van de functionele modulen zelf, is echter ook een nadere verdeling mogelijk. Het gaat hier bijvoorbeeld om de algoritmen van grafische functies, zoals Gouraud-schakering. Deze algoritmen bestaan uit een groot aantal sequentieel uit te voeren basisbewerkingen. Normaal gesproken voert een van de functionele eenheden, de vermenigvuldiger bijvoorbeeld, ook een van die instructies uit terwijl de rest de resultaten afwacht.

Arcobel heeft echter een architectuur ontworpen waarbij de toewijzing van de basisinstructies aan de afzonderlijke functies gelijktijdig geschiedt. Elke eenheid heeft daartoe een klein codeveld in een overkoepelende instructie met een standaardlengte van 64 bit. Onderlinge afstemming geschiedt via acht interne bussen (voor acht functionele eenheden).

#### Pijplijn

De modulen functioneren ten opzichte van elkaar als substations met deeltaken zodat met recht kan worden gesproken van een parallelle processor. Er is niet alleen sprake van een verdeling van de instructies tijdens dezelfde klokcyclus, er is ook sprake van opdeling van instructies over de verschillende functionele eenheden.

Juist pixelstromen, met hun regelmatige karakter, lenen zich bijzonder goed voor deze werkwijze. Zo wordt het mogelijk een pijplijn op te zetten die de beeldpunten naar en door een of meer functionele eenheden in de Imagine voert. In feite betekent dit een verdere verfijning van de pijplijn-architectuur zoals die in alle huidige Risc- en vectorprocessoren zit. Het 64-bit instructieformaat vormt daarbij een brug tussen twee werelden: die van de conventionele, algemeen bruikbare CPU en die van de applicatiespecifieke hardware.

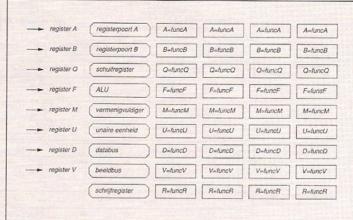

#### Hisc

Het programmeren wijkt op zich niet af van conventioneel coderen. Daarmee komt een potentiële spelbreker om de hoek kijken: de software. Even lijkt het erop dat de ontwerpers een knieval doen voor eventuele skepsis. "Nieuwere optimaliserende compilers met voldoende data-afhankelijkheidsanalyse," laat het bedrijf in eigen documentatie weten: "kunnen zorgen voor efficiëntere en snellere objectcode." Betekent dit dan dat het oorspronkelijke uitgangspunt, optimale benutting van de hardware, toch nog enige nuancering behoeft?

Wie een relativering aantekent bij de optimale benutting van de hardware, kan van De Vries eenzelfde opmerking terugkrijgen. Die nuance luidt in één woord: Hisc. Hisc staat voor Hierarchical Instruction Set Computer en behelst, zoals de term al aangeeft, voor een hiërarchie van verschillende programmeerniveaus. De hoogste twee niveaus zijn min of meer standaard voor elke processor: een hogere programmeertaal als C en de assembleertaalopdrachten. Daarna volgen nog twee extra lagen: ba-

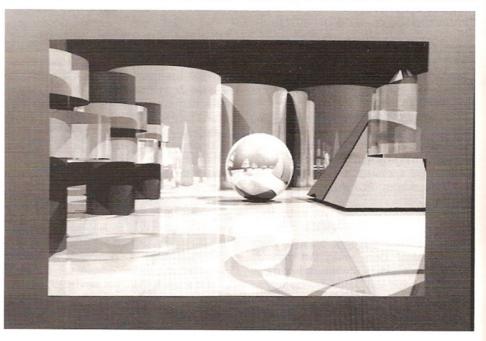

Kenmerkende toepassing voor de Imagine: professionele DTP met bijbehorende verwerking van CMYK-afbeeldingen op drukkerskwaliteit.

sisopcodes ('free pipeline') en de uitgebreide instructies. Deze laatste 'extended' codes buiten alle aanvullende mogelijkheden tot in detail uit door gebruikmaking van besturingsregisters in de functionele eenheden (ref. 1).

#### Programmatuur

Alle softwarelagen zijn bereikbaar vanuit een hogere programmeertaal door middel van de zogeheten inline-opdrachten. "Op assemblerniveau programmeren zal niet ieders dagelijks werk zijn," aldus De Vries: "maar een goede programmeur moet binnen twee maanden behoorlijk uit de voeten kunnen met de Hisc-opzet. Eén maand om vertrouwd te raken met de mogelijkheden en nog een maand om de laatste procenten uit de processor te kunnen halen."

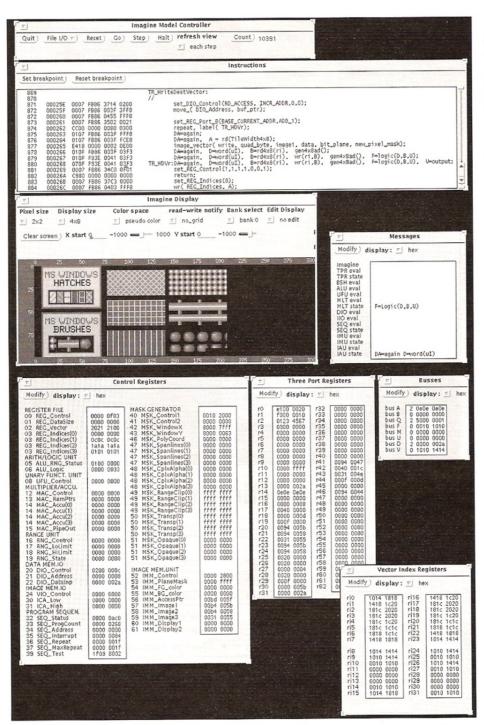

Ten Den illustreert het programmeren volgens het Hisc-concept aan de hand van het overzetten van een bestaande applicatie. "Je begint met de bestaande C-code, die compileer je voor de Imagine. Dan begint het optimaliseringsproces. Je identificeert elementaire functies die de meeste verwerkingstijd vergen en die vervang je door inline statements. De functies kun je nu op elk programmeerniveau uitwerken. Vanaf dat punt werk je tien maal sneller dan met een gewone processor." Hij laat niet na in dit verband ook de "gebruiksvriendelijke programmeeromgeving" te noemen.

#### **Dataflow**

Hiermee is een grof maar aannemelijk beeld geschetst van een nieuwe superprocessor. Toch blijft de vraag hoe een ploeg van zes man gerenommeerde namen als Intel achter zich laat. Ten Den's verhaal komt neer op een mengeling van omstandigheden die tezamen uiteindelijk een positief effect hebben gehad.

Achteraf blijkt dat het ontwikkelproces, gestart in juni 1991, nogal sterk techniekgeoriënteerd is geweest. Ten Den: "Vanuit commercieel standpunt misschien niet zo verstandig maar achteraf zeker een pluspunt. We hebben de tijd genomen om technische obstakels uit de weg te ruimen."

Deze benadering tijdens de ontwikkelfase laat zich onder andere verklaren door het opkopen van de boedel van het gefailleerde Dataflow Technology Nederland (DTN), waar ook De Vries werkte (ref. 2). Het uitgangspunt was om de bij DTN aanwezige, veelbelovende kennis over grafische apparatuur en beeldverwerking te benutten. Een duidelijk beeld over een marktrijp produkt D

had men toen eigenlijk nog niet. Aanvankelijk was er sprake van het plan om drie grafische dataflowkaarten tot één kaart terug te brengen. Gaandeweg evolueerde dit tot het idee van een enkele ehip. Daarbij raakte het dataflowprincipe wat op de achtergrond, hoewel dataflowgrafen bij het programmeren zeker terugkeren.

#### **Spartaans**

Een ander punt is de "Spartaanse werkwijze", zoals Ten Den het omschrijft. De Imagine is het werk van slechts vier ontwerpers, met daarnaast De Vries als geestelijk vader vanuit zowel hardware- als softwareperspectief. Dit is een totaal andere situatie dan bij Intel, waar tientallen specialisten aan volgende generaties processoren werken.

Niet alleen is het gelukt om mensen van een bepaald kaliber te verzamelen maar volgens De Vries was er ook "echt sprake van een team". De onderlinge enthousiasmering – natuurlijk niet echt verwonderlijk bij zo'n uitdagend project – heeft heel wat duitjes (dat wil zeggen: late uurtjes) in het zakje gedaan.

Kostenbewaking was volgens Ten Den tijdens het hele project essentieel. "Als het langer gaat duren dan gedacht, moet je heel bewust met je mogelijkheden omspringen." Vanuit deze gedachte laat zich ook de eigenzinnige ontwerpmethodiek verklaren.

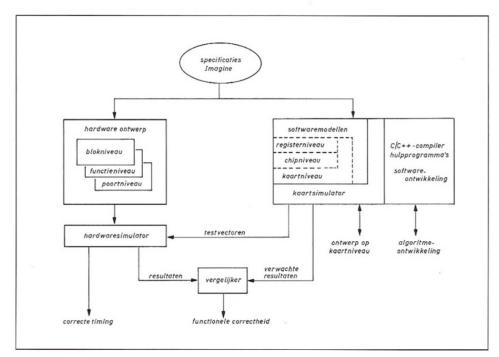

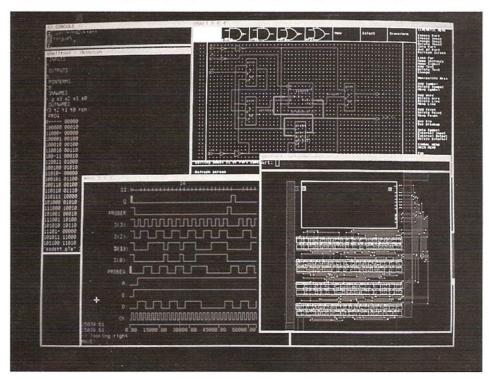

Door de hardwaresimulator van LSI te voeden met de door het softwaremodel gegenereerde testvectoren, was 1:1-verificatie mogelijk zonder (dure) prototypen te vervaardigen.

#### Kostenbesparing

De hele processor is, inclusief bijbehorende omgeving, eerst volledig softwarematig beschreven op functioneel niveau. Was dit aanvankelijk bedoeld om algoritmen van grafische functies mee te ontwikkelen, geleidelijk groeide het programma uit naar een testmodel voor de chip zelf (fig. 1).

Door de hardwareontwerpsimulator van LSI Logic (de onderneming die de chip seriematig gaat produceren) te voeden met dezelfde testvectoren als het softwaremodel, kon zonder de chip feitelijk te produce-

Fig. 1. Het softwaremodel is geleidelijk aan uitgegroeid tot een compleet testmodel.

ren worden nagegaan of het IC-ontwerp tot op registerniveau sluitend is. De met het eigen model gegenereerde teststimuli leidden "na tientallen iteraties" (Ten Den) tot een 1:1-verhouding met de hardwaresimulator.

Omdat LSI's software de werking op transistorniveau garandeert, kon het ontwerp functioneel correct worden gemaakt zonder dat daar prototypen aan te pas hoefden te komen. Dit betekende een aanmerkelijke besparing op de ontwikkelkosten. Ten Den: "Met dat model was het ook mogelijk tijdig en zonder al te veel moeite wijzigingen in de specificaties aan te brengen. Nu bleek in een zeer vroeg stadium dat we bepaalde zaken nog eleganter konden implementeren."

#### Grenzen

Ook op een andere, eigenlijk erg voor de hand liggende, manier stond kostenbeheersing centraal: nieuwe implementatiemethoden zijn nooit serieus overwogen, de bestaande siliciumtechnologie moest voldoen. Kennelijk had Arcobel voldoende vertrouwen in de eigen creativiteit om dit varkentje te wassen: wie op basis van bestaande technieken toch een aanmerkelijke prestatieverbetering wil realiseren, moet immers durven denken 'vanaf het punt nul' om verrassende oplossingen te creëren.

Dit is in feite ook wat Anton Montagne, internationaal docent elektronisch ontwerpen, betoogde in een vorige ELEKTRONI-

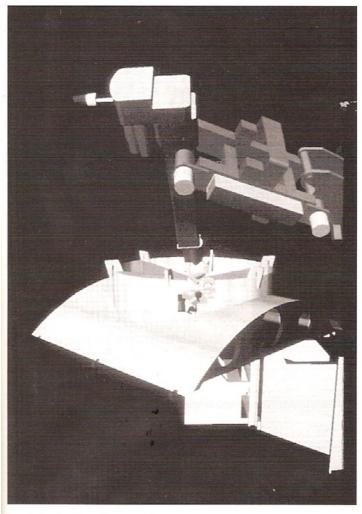

De uit te brengen PCkaart met Imagine brengt onder andere volwaardige 3D-CAD binnen bereik.

CA (ref. 3). Zijn vrij vertaalde credo is: verken eerst nadrukkelijk de mogelijkheden van de bestaande technologie alvorens over te stappen op "een betere fabricagemethode". Montagne: "Ontwerptechniek houdt in dat je de grenzen van de technologie probeert te benaderen. Dan haal je met een zo klein mogelijke claim op de techniek een maximaal resultaat." Volgens hem komt het in de praktijk niet zo gek vaak voor dat ontwerpers vanaf 'een punt nul' vertrekken.

Dit gegeven zou echter wel voor een groot gedeelte de eigenzinnigheid van de Imagine kunnen verklaren. De Vries hierover: "In ieder geval wilden we niet uitgaan van het 'me too'-effect. Zo van: de anderen hebben iets, kunnen wij niet iets soortgelijks maken? Vaak ben je dan duur en als je vervolgens op de markt komt, is je produkt ook al weer achterhaald."

#### Produktie

Hoe dit ook zij, LSI Logic heeft inmiddels de laatste hand gelegd aan de layout. De component wordt vanaf mei officieel in produktie genomen. Volgens Ten Den is het na-

drukkelijk de bedoeling niet alleen een chip op de markt te brengen. Een SVGA-compatibele PC-kaart komt gelijktijdig beschikbaar. Daardoor ontstaan twee marktsegmenten: de grote fabrikanten die hun eigen produkten maken en de brede markt met PC-gebruikers.

Ten Den verhult niet dat met verschillende fabrikanten al contacten bestaan over inbouw van de Imagine in specifieke apparatuur. Hij noemt uiteraard geen namen, maar geeft wel voorbeelden in welke richting wordt gedacht. "Hij zou bijvoorbeeld goed werk kunnen doen in DTP-machines en grafische werkstations. Maar denk ook aan 'embedded' gebruik in bijvoorbeeld een kleurenlaserprinter of aan 'image engines' in CD I-applicaties. Trouwens: je kunt ook denken aan gevanceerde spelcomputers."

Hij noemt de huidige contacten zeer hoopvol, temeer omdat de potentiële klanten veelal af moesten gaan op het softwaremodel. Ondanks de snelheidsbeperkingen die een werkstation biedt om een reële indruk van de prestaties te krijgen, heeft een aantal prospects toch zijn vertrouwen in het produkt uitgesproken. "Dat geeft inderdaad vertrouwen, want als je het overdreven stelt hebben we een tijdje in gebakken lucht gehandeld."

#### PC-kaart

Het tweede produkt wordt een uitbreidingskaart voor PC's en deze zal vooral moeten bijdragen aan de naamsbekendheid in brede kring. Ten Den: "De keuze om de processor toch ook op een PC-kaart uit te brengen is mede ingegeven door het feit dat de grafische software voor de PC het niveau benadert van professionele systemen. Hierbij kun je denken aan 24-bit kleuren-DTP, driedimensionale CAD, animaties en studiokwaliteit video. Onze kaart brengt de verwerkingskracht van een PC ook hardwarematig op dit niveau."

Met de PC-kaart zal volgens Ten Den vanzelf blijken dat de CPU zijn belofte waar maakt. "Een reactie in de trant van 'zoiets bestaat niet!' kan ik me levendig voorstellen. Maar met een voor iedereen verkrijgbare PC-print ben ik ervan overtuigd dat zo'n reactie al snel achterhaald is. Geloofwaardigheid moet je afdwingen. Gewoon met behulp van resultaten."

De Vries stelt dat de uitbreidingskaart een belangrijke bijdrage kan leveren aan de softwareontwikkeling voor de processor. Weliswaar draaien al enkele standaardpakketten op de Imagine maar dat neemt niet weg dat nieuwe hardware nieuwe software moet uitlokken. Dat verhoogt weer de marktwaarde van zowel de kaart als de chip.

De geestelijk vader van de chip sluit trouwens niet uit dat er ook klanten zullen zijn die kaarten aan elkaar willen koppelen. Twee of vier met elkaar verbonden kaarten maken bijvoorbeeld zware driedimensionele simulatietaken mogelijk. De snelheidswinst is bij koppeling nagenoeg lineair, de softwareaanpassing nagenoeg afwezig.

Over de prijs van de chip laten beide heren zich nog even niet uit. Ten Den geeft als indicatie een bedrag in de richting van "een high-end Risc". De Vries: "Dat lijkt ons een reële marktwaarde. Uiteindelijk spreek je hier over een chip die een flink aantal jaren mee zal gaan. Je hebt een duidelijke voorsprong, zowel qua efficiency als programmeerbaarheid."

#### Literatuur:

[1.] Theo van Gelder: Grafische superprocessor 'hergebruikt' transistoren, Elektronica 1994, nr. 6.

[2.] Robert van der Zwan: Dataflow wordt marktrijp, Elektronica 1989, nr. 20.

[3.] André Weigand: Ontwerptechniek moet grenzen van technologie benaderen, Elektronica 1994, nr. 3.

Imagine's Hisc houdt flexibele hardware programmeerbaar

# Grafische superprocessor 'hergebruikt' transistoren

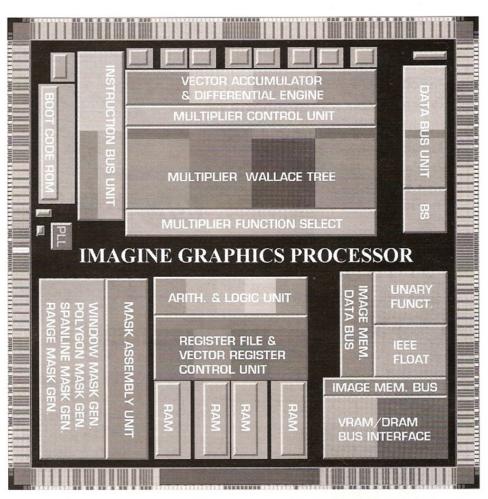

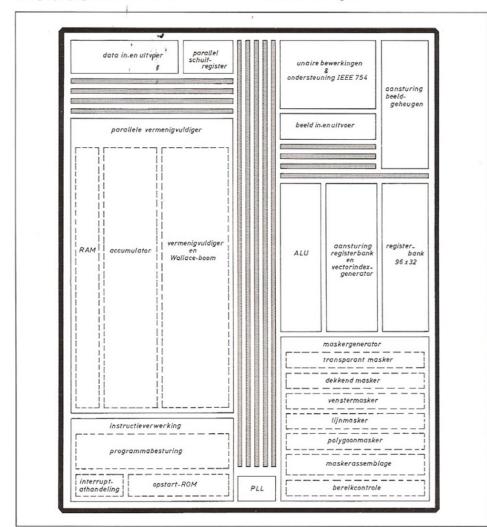

De snelste grafische processor van dit moment komt uit Den Bosch. Dat claimen althans de ontwerpers van Arcobel Graphics. Hun Imagine haalt op een klokfrequentie van 67 MHz een piek van 330 Mips bij 32-bit bewerkingen maar kan dezelfde hardware ook gebruiken om er 8-bit data mee te kraken en doet dat dan in een tempo van 8000 Mips. Daarmee loopt de chip vijf tot twintig maal harder dan de vergelijkbare Risckrakers van DEC, HP, Intel en Mips. Het gaat echter nog steeds om een algemeen bruikbare CPU die weliswaar duidelijk is toegesneden op grafische taken maar die zich niet beperkt tot een enkele toepassing. De truuk zit in de manier waarop de Imagine is opgebouwd. In de eerste plaats kunnen alle afzonderlijke functieeenheden op de chip geheel onafhankelijk werken, mede door een achttal gescheiden datakanalen. Daarnaast kan het gedrag van die modulen tot op zeer laag niveau worden geprogrammeerd. Dat introduceert een extra niveau parallelliteit, waardoor de 32-bit ALU zich bijvoorbeeld als twee 16-bit of vier 8-bit ALU's kan gedragen. De keerzijde van zo'n laag-niveau benadering is het veel ingewikkelder programmeerwerk. Daarom hebben de ontwikkelaars het Hisc-concept ingevoerd: hiërarchische instructiesets die, al naar gelang de gewenste mate van optimalisatie, door middel van C- en assembleertaalcode afdalen van Risc- en Cisc- tot register- en bitniveau. Op die manier kunnen complexe functies worden geprogrammeerd op parallelle datastromen.

Arcobel's Imagine bestaat momenteel alleen nog als ontwerpbestand in LSI's Asic-programmatuur. Volgende maand moet deze producent beginnen met bakken.

Grafische bewerkingen blijven een crime voor de doorsnee verwerkingseenheid. En dan gaat het niet eens zozeer om de complexiteit van de operaties maar om de veelheid ervan. Een professioneel DTP-plaatje in kleur, 32 bit per beeldpunt, kost bij 600 dpi en 10×10 cm ruim 21 Mbyte. Ophalen en weergeven gaat nog wel maar het geduld oefenen voor de opmaker aan het werkstation begint pas wanneer zo'n afbeelding bijvoorbeeld moet worden geroteerd en opnieuw gerasterd.

Het zijn deze en soortgelijke toepassingen waarvoor Arcobel Graphics de Imagine heeft ontworpen. Dat deze processor hoofdzakelijk is bedoeld voor grafische taken en beeldbewerking komt bijvoorbeeld

naar voren uit de interne hardware, die onder andere eenheden voor vermenigvuldigen, conversies en het genereren van diverse maskers omvat. Ook stuurt de chip zelf VRAM- en DRAM-beeldgeheugen aan. Als voorbeelden van toepassingen worden grafische werkstations, kleuren-laserprinters, digitale signaalverwerking, DTP-hardware en beeldherkenning/visuele inspectie genoemd. In multiprocessorconfiguraties valt te denken aan geavanceerde 3D CAD-systemen, real-time video, vluchtsimulatoren en dergelijke.

#### Meerlaags superscalair

Wat veel van de jongere generaties CPU's al kennen, is in de Imagine nog een stukje >

verder doorgevoerd, namelijk superscalaire verwerking. In de eerste plaats geldt deze eigenschap voor alle acht interne functie-eenheden. Deze kunnen volledig onafhankelijk van elkaar opereren en derhalve ook gelijktijdig taken uitvoeren.

Ook ingebedde toepassingen als kleurenlaserprinters behoren tot de mogelijke toepassingen.

De ontwerpers zijn echter nog een stap verder gegaan, een essentiële waar het de bereikte prestaties betreft, door ook de werking van de functieblokken zelf vergaand programmeerbaar te maken. Op die manier kan bij kleinere woordbreedten ook de inherente parallelliteit van de 32-bit eenheden worden benut. Het meest extreme voorbeeld daarvan is de 32-bit vermenigvuldiger die bij 8-bit waarden gelijktijdig zestien multiplicaties en twaalf optellingen kan uitvoeren.

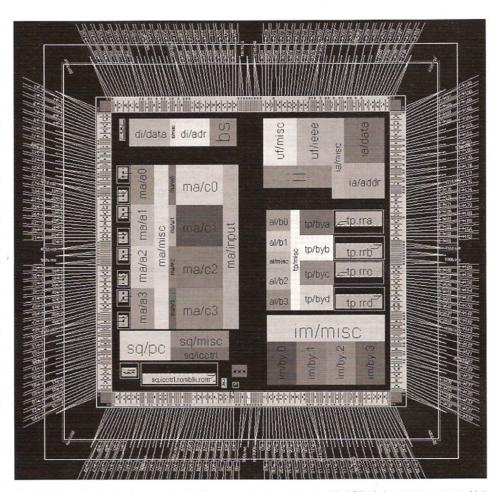

De interne besturings- en functie-eenheden zijn onder te verdelen in vier groepen. In de eerste groep bevinden zich een achttal dataverwerkingsfuncties, die zijn gericht op taken als optellen, vermenigvuldigen, schuifoperaties en dergelijke (fig. 1). Acht bussen transporteren de gegevens tussen deze modulen. Daarbij kunnen ze, al naar gelang het programmeerniveau, gescheiden werken of gegroepeerd in een of meer deelpijplijnen voor bijvoorbeeld vectorbewerkingen.

Een uit verschillende subeenheden opgebouwde maskergenerator vormt de tweede categorie. Deze combineert lijn-, polygoon, venster- en vrije-vormpatronen met voorgrond- en achtergrondinformatie tot samengestelde maskers. Hij vormt daarmee de belangrijkste bron voor het genereren van grafische elementen op de chip.

De derde groep zorgt voor het afhandelen van instructies en voorvallen die de loop van het programma beïnvloeden. Dit zijn bijvoorbeeld als sprongopdrachten, routineaanroepen en interrupts maar ook het routeren van vectorstromen en die zaken regelt de programmabesturing.

Tenslotte zorgt de interface met het beeldgeheugen voor de aansturing van VRAM's en DRAM's. Daarbij kan hij verschillende paginerings- en toegangsmethoden hanteren. Ook driepoorts videogeheugens kunnen worden aangesloten.

#### Gegevensverwerking

Hoe de functie-eenheden en de verbindende databussen zijn gegroepeerd, valt te zien in figuur 2. Alle acht kanalen werken met eenrichtingsverkeer: ze worden elk vanuit één module aangestuurd. Deze doen dat door aan het eind van iedere cyclus het resultaat van de bewerking in het uitgangsregister te zetten. Afhankelijk van het type operatie kunnen de andere eenheden die uitkomst inlezen als operand bij een volgende bewerking.

Deze opbouw staat volledige parallelliteit toe. Ook meervoudige vectoroperaties die anders een programmalus vereisen, zijn hiermee terug te brengen tot één cyclus. Dit gebeurt door de betrokken modulen zodanig te schakelen dat ze een pijplijn voor de datastroom vormen. De keten produceert elke processorslag een volgende einduitkomst, althans zolang alle gekoppelde eenheden dat tempo kunnen volhouden

Een ander verbindend element vormt de

registerbank. Deze bevat 96 ingangen die als enkelvoudig 32-bit, dubbel 16-bit of viervoudia 8-bit woord kunnen worden gezien. Drie poorten maken het mogelijk om gelijktijdig twee leestoegangen (poorten A en B) en een schrijfactie (poort C) uit te voeren. Van de 96 registers zijn de locaties 0..62 rechtstreeks toegankelijk aan de hand van drie 6-bit verwijzingen in de opcode (aanspreken van register 63 heeft het effect van een NOP-opdracht). De overige 32 ingangen worden geadresseerd via de vectorindexgenerator. En omdat elk woordsegment binnen de registers afzonderlijk is te selecteren, kan de vectorindexgenerator per cyclus tot een maximum van twaalf lo- D

Fig. 1. Chipindeling van de Imagine.

Fig. 4. Zestien min of meer onafhankelijke cellen vormen de Wallaceboom.

> caties genereren: vier bytesecties voor elk van de drie poorten.

#### Schuifregister

Het schuifregister verplaatst in één klokcyclus 32 bit aan gegevens 1 tot 32 posities naar links of naar rechts. Ook hier kan de informatie zijn gegroepeerd in 1, 2 of 4 secties van respectievelijk 32, 16 en 8 bit. De eenheid kent drie vormen van verschuiven: logisch (zonder teken), numeriek (met teken) en roterend.

Zoals in figuur 2 valt te zien, komen de operanden van ofwel de ALU ofwel de registerbank. Hoe het schuifregister zich gedraagt ten aanzien van de woordbreedte, hangt af van de manier waarop de operanden zijn ingedeeld. Het aantal te schuiven posities wordt eveneens uit een register opgehaald. Daarbij is het toegestaan een groter aantal dan 32 op te geven zonder dat dit in een verkeerde uitkomst resulteert.

#### ALU

In de meeste opzichten functioneert de ALU als een conventionele numerieke/logische eenheid. De gebruikelijke zestien logische bewerkingen worden onder-

steund, samen met een vijftiental numerieke functies als optellen, aftrekken, ophogen en verlagen. Daarbij kan het in de vorige cyclus gegenereerde rest- annex leen-bit worden gebruikt in combinatie met de operanden van de volgende operatie.

Een extra voorziening is de zogeheten parametrische logische functie. Hiermee kan aan de hand van de inhoud van een 8-bit register een willekeurige combinatie van 256 mogelijke logische bewerkingen worden uitgevoerd op drie operanden. Als toepassing hiervoor worden grafische bedieningssinterfaces als X Window en MS-Windows genoemd. Deze standaarden specificeren dat logische en grafische operaties in elke combinatie mogelijk moeten zijn. Ook kan de parametrische functie worden gebruikt voor het realiseren van schuiven, maskeren en een samenvoeg- of vergelijkingsbewerking in een enkele cyclus.

Zoals te verwachten valt, kan ook de ALU zich gedragen als een enkelvoudige dan wel als een dubbel of viervoudig parallelle eenheid voor 32-, 16- en 8-bit waarden. De betreffende operanden komen binnen bij een van de twee ingangsregisters, R en S. Deze kunnen gegevens selecteren van de

A-, D-, M- en Q-bus respectievelijk B-, F-, Uen V-bus (zie figuur 2). Daarbij bepaalt de S-operand het datatype, tenzij het om een bewerking gaat die alleen het R-register gebruikt.

Met vier toestandsbits – nul, negatief, overloop, resultaatteken – wordt het resultaat van de ALU-operatie aangeven. Deze staan voor elk van de parallelle bewerkingen in een 16-bit toestandsregister, waar voor iedere 8-bit sectie een afzonderlijk veld is gereserveerd.

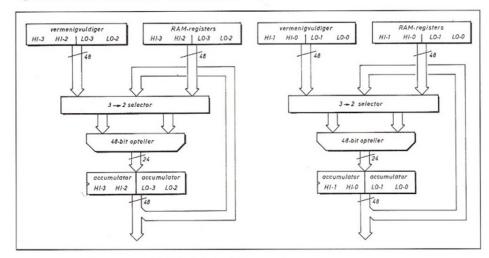

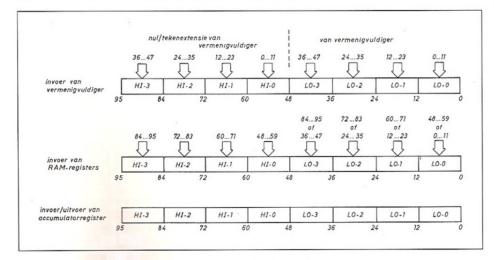

#### Vermenigvuldiger

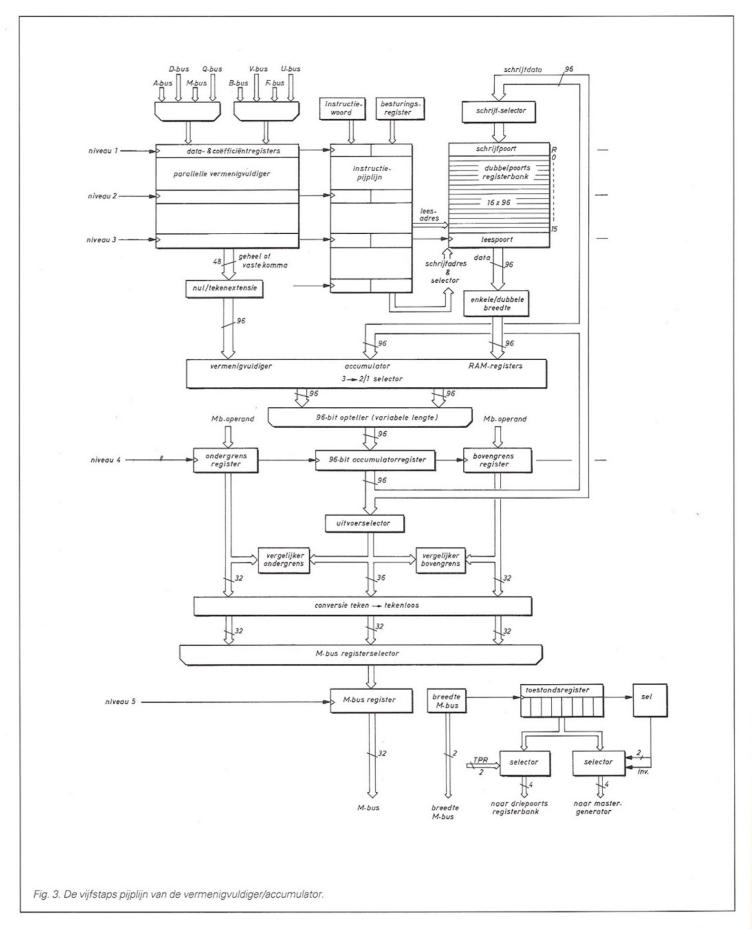

Een van de meest complexe circuits van de Imagine is de vermenigvuldiger met accumulator (fig. 3). Geheel in lijn met de overige chipmodulen is voorzien in 32-, 16- en 8-bit bewerkingen. Alle gegevens lopen door de als vijfstaps pijplijn geconfigureerde eenheid. Het duurt derhalve vijf klokcyclussen tot de uitkomst beschikbaar is, onafhankelijk of de vermenigvuldiging al dan niet wordt niet gecombineerd met accumulatorfuncties en bereikcontrole.

Er kan worden gewerkt met getallen met en zonder teken of een combinatie daarvan en de waarden kunnen worden geïnterpre-

## Hisc-programmeren

Hoe efficiënt je een processor ook kan maken door hem op een laag hardwareniveau configureerbaar te maken, je hebt daar weinig aan als op die manier een CPU ontstaat die niet meer aan de praat te krijgen is vanwege een onmogelijke hoeveelheid programmeerwerk. De ultieme flexibele en optimaliseerbare chip is een verzameling van enkele honderdduizenden of miljoenen losse transistoren die softwarematig tot de gewenste circuits worden samengevoegd. De onmogelijkheid om daar code voor te schrijven zal zo'n IC snel in het archief met interessante curiosa doen belanden. Op veel kleinere schaal kampt de Imagine met een vergelijkbaar probleem: op laag niveau is het aantal mogelijkheden zo groot dat het schrijven van een optimale routine een zeer lastige klus is. Daar hebben de ontwerpers een oplossing voor bedacht: een hiërarchische instructieset, kortweg Hisc.

Fig. B. De basisinstructies hebben een afzonderlijk veld voor elke functie-eenheid.

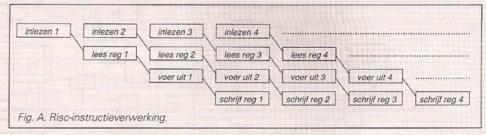

Zoals de term Hisc al aangeeft, wordt de Imagine geprogrammeerd op meerdere niveaus. Bovenin de hiërarchie staan C-compiler en assembleertaal. Die maken de processor net zo toegankelijk voor programmeurs als conventionele Risc- en Cisc-verwerkingseenheden. Op deze niveaus is het echter niet mogelijk om de parallelliteit en de flexibiliteit van de hardware volledig te benutten.

De resulterende Risc-achtige opcodes doorlopen de gebruikelijke lees/decodeer/schrijf-cyclus (fig. A). Hieruit vloeit dan ook geen snelheidswinst voort ten opzichte van andere Risc-CPU's. Hoogstens zorgt de interne taakspecifieke hardware voor een voorsprong op het grafische vlak.

Compiler en assembleertaal genereren de zogenoemde basisinstructies. Deze com-

mando's gaan een stap verder omlaag in de rangorde. Ze bevatten een afzonderlijk opcodeveld voor elk van de functie-eenheden van de chip inclusief de manier waarop deze aan de andere eenheden zijn gekoppeld (fig. B). De verwerkingspijplijn ligt dus niet vast maar hangt af van de in de instructie opgegeven routering. Dit daarom 'free pipeline' genoemde niveau maakt het mogelijk om de functie-eenheden doelmatig parallel te laten werken (fig. C en D). Dat kost wel meer programmageheugen: door de opdeling in velden zijn de opcodes 64 bit land.

### Vectorverwerking

Op het laagste trede van de hiërarchie staan de zogeheten uitgebreide ('extended') instructies, die in samenwerking met de besturingsregisters het gedrag van

Fig. 5. Woordindeling bij dubbele 48-bit ALU-bewerkingen.

Fig. 6. Functieschema van de ALU bij dubbele 48-bit operaties.

Fig. 7. Als figuur 5 maar dan met een viervoudige 24-bit berekening.

teerd als gehele, vaste-komma en (eventueel afgeronde) genormaliseerde vastekomma getallen. In totaal telt het repertoire 786 verschillende operaties.

Verder is de Wallace-boom in staat om 16-

bit complexe getallen met elkaar en 8-bit matrices met vectoren te vermenigvuldigen. In het laatste geval worden 28 berekeningen gelijktijdig uitgevoerd: zestien multiplicaties en twaalf optellingen. De boom is in feite ook geconfigureerd als 16 losse 8bit vermenigvuldigingscellen, alleen zodanig dat ze bij grotere woordbreedten efficiënt kunnen samenwerken (fig. 4). Toepassingen die zich goed lenen voor dergelijke fijnmazig parallelle combinatiebewerkingen zijn kleurtransformatie, convolutie, correlatie en real-time Phong-schakering.

De data/coëfficiëntregisters tussen de ingangsbuffers van de bussen en de vermenigvuldiger functioneren als invoerpijplijn. Ze hebben een breedte van 128 bit en kunnen zo een 4x4-matrix met 8-bit cellen als één woord transporteren. Daarbij is het bovendien mogelijk om onderweg een rotatie uit te voeren die rijen en kolommen verwisselt.

#### Accumulator

De vermenigvuldiger/accumulator werkt intern met 48-bit resultaten (of dubbele 24-bit dan wel viervoudige 12-bit waarden). Daarvan kunnen er twee gelijktijdig worden getransporteerd via de 96-bit datakanalen. Deze ten opzichte van de overige eenheden grotere woordbreedte verhoogt de nauwkeurigheid waar het de verwerking van meerdimensionale pixels en kleurgecodeerde informatie betreft.

Hetzelfde geldt voor het accumulatordeel achter de vermenigvuldiger, dat diverse doelen kan dienen. Als viervoudige 24-bit of dubbele 48-bit accumulator (zie figuur 5, 6, 7 en 8) ondersteunt hij grafische bewerkingen als driedimensionale Gouraudschakering en de opslag van Z-bufferinformatie. Een speciale registerbank met 16 woorden van 96 bit zorgt voor de opslag van tijdelijke accumulatorwaarden. Afzonderlijke lees- en schrijfpoorten maken gelijktijdig ophalen en wijzigen van variabelen mogelijk.

Daarnaast is de accumulator in staat om samen te werken met de geheugenaansturing voor het genereren van twee- en driedimensionale adressen. Gebeurt dat incrementeel, als onderdeel van een stroom beeldinformatie, dan kan elke klokcyclus een meerdimensionaal adres worden gegenereerd. Het aansturen van Neorde locaties – bijvoorbeeld van 2D- en 3D-krommen en oppervlakken – duurt N+1 cyclussen. Deze eigenschappen zijn te gebruiken bij hogere-orde textuurprojectie en voxel-bewerking:

#### Bereikcontrole

Voordat de door de vermenigvuldiger/accumulator gegenereerde uitkomst wordt geconverteerd naar een tekenloze waarde vindt nog een bereikcontrole plaats. In dat stadium is nog de overloopinformatie beschikbaar die nodig is om te bepalen of de

Fig. C. Door de afzonderlijke aansturing en routering maken de eenheden als het ware deel uit van een vrij programmeerbare pijplijn.

Fig. E. Vectorgeoriënteerde benutting van de functie-eenheden.

waarde tussen de gedefinieerde onder- en bovengrens ligt. Zo'n limitering is van nut bij onder andere driedimensionale Z-bufferbewerkingen, kleurverzadiging bij conversie van RGB naar YUV, het omzetten van interliniëring naar niet-interliniëring, beeldvergelijking en dergelijke.

Wanneer de bereikcontrole is ingeschakeld, neemt hij altijd het datatype van de accumulatoruitgang over (8-, 16-, 32-bit, met/zonder teken). De onder- en bovengrens zijn in principe constante waarden maar het is ook mogelijk om deze elke klokcyclus te verversen met de data van de Mb-ingangspoort van de vermenigvuldiger.

Twee toestandsbits geven aan hoe het geteste accumulatorresultaat zich verhoudt tot de twee limieten (binnen bereik, te hoog, te laag, zowel te hoog als te laag). Als de uitkomst binnen het opgegeven bereik moet blijven dan wordt, in het geval van een maximum- of minimumoverschrijding, de betreffende limiet naar de uitgang gestuurd in plaats van de testwaarde.

#### Unaire bewerkingen

De laatste gegevensverwerkende eenheid van de Imagine is bedoeld voor het converteren van data. Hij heeft de naam unaire module gekregen omdat het gaat om bewerkingen op enkelvoudige operanden.

Dat betreft bijvoorbeeld de omzetting van binair naar unair (lineair), het aangeven van de positie van de meest significante 1, het bepalen van de absolute waarde of het teken en het omdraaien van de bitvolgorde in een woord. Zoals bij alle functies van de chip kan ook hier een woord 32, 16 en 8 bit breed zijn.

Hoewel het de bedoeling is om toekomstige versies van de processor daar wel mee uit te rusten, is er nu nog geen aparte hardware voor IEEE 754-conforme drijvendekomma berekeningen. Deze worden nu in 32 bit uitgevoerd als gehele getallen in samenwerking met een kleine eenheid die de conversie, het bijhouden van de exponent en de in de numerieke standaard gedefinieerde uitzonderingstoestanden afhandelt.

Op deze manier haalt de CPU, ondanks dat de extra circuits maar 3% van de chip beslaan, bij drijvende-komma operaties prestaties die op het niveau van een 100-MHz 80486 liggen. In combinatie met geoptimaliseerde macro's kunnen speciale 3D-functies, zoals een driedimensionale coördinaattransformatie, even snel worden uitgevoerd als op dit punt zwaarder toegeruste processoren zoals Intel's 80860 en Mips' R4400. Zo duurt een homogene transformatie plus perspectieve deling 60 klokcyclussen.

#### Maskergenerator

Min of meer losgekoppeld van de cluster gegevensverwerkende eenheden verricht de maskergenerator een serie specifiek grafische functies (zie figuur 1). Zo kan hij de omtrek van alfanumerieke tekens vastvoorgrond/achtergrondvergelijkingen (Z-buffer) en diverse typen polygoon-, venster- en vrije-vormmaskers creëren. In veel toepassingen zullen meerdere van die bewerkingen gelijktijdig nodig zijn. Een voorbeeld daarvan is de weergave van een Gouraud-geschakeerd polygoon een venster. Dit vergt behalve een kleurmasker ook nog een controle welke pixels in dan wel buiten het venster liggen, of ze in het driedimensionale bereik vallen en of ze tot de voorgrond behoren.

Om deze functies in hetzelfde tempo te kunnen uitvoeren als de overige bewerkingen, is de maskergenerator opgebouwd uit

Fig. 8. ALU-functieschema voor de viervoudige 24-bit bewerking.

zeven onafhankelijke subeenheden. Daarvan legt het venstermasker vast wat de gebieden zijn waarbinnen de andere bewerkingen moeten vallen. Hij doet dit door wijzigingen toe te staan bij pixels die binnen de gedefinieerde grenzen liggen en de erbuiten liggende te blokkeren.

De bereikcontrole werkt aan de hand van voorgedefinieerde patronen in plaats van meetkundige informatie. Een van de belangrijkste toepassingen daarvoor is het genereren van lettertekens. Deze subeenheid dient tevens voor de controle op driedimensionale pixelgegevens als kleur en Z-bufferinhoud.

Het lijnmasker repeteert horizontaal een gedefinieerd patroon tussen een opgegeven begin- en eindpunt. Hij kan tot vier lijnen gelijktijdig genereren en ondersteunt zo bijvoorbeeld het creëren van polygonen. Zolang een willekeurige vorm langs elke horizontale lijn waaruit hij is samengesteld geen onderbrekingen bevat, kan hij met behulp van het lijnmasker worden aangemaakt.

Voor het genereren van elementen waarvoor de lijngenerator niet geschikt is, kan het polygoonmasker worden ingezet. Bij niet-samenhangende symbolen – bijvoorbeeld Chinese tekens – is het vaak lastig om na te gaan of een beeldpunt hier wel of niet deel van uitmaakt. Het polygoonmasker bepaalt dit door te tellen hoeveel contourovergangen er op de horizontale lijnen liggen die door het betreffende pixel gaan.

De maskerassemblage-eenheid legt venster-, vrije-vorm-, lijn- en polygoonmaskers over elkaar. Het resultaat gaat naar het transparante en/of dekkende masker, waar >

|         | THREE PORT REGISTER FILE                             |        | CONTROL REGISTERS                                                                                                          |

|---------|------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------|

| ro      | System context structure ptr                         | crO    | register file control register                                                                                             |

| rl      | Graphics context structure ptr                       |        | data size monitor                                                                                                          |

| r2      | interrupt stack pointer                              | cr2    | vector index control register                                                                                              |

| r3      | interrupt temporary save area                        | cr3.0  | vector indices port A                                                                                                      |

| 14      | interrupt temporary save area                        | cr3.1  | vector indices port B                                                                                                      |

| r5      | interrupt temporary save area                        | cr3.2  | vector indices port C                                                                                                      |

| 16      | stack pointer used by C and ASM                      | cr3.3  | vector write enable & delayed status                                                                                       |

|         | frame pointer used by C and ASM                      | cr5    | ALU and RC status register                                                                                                 |

|         | return value register                                | cr6    | three operand logic function                                                                                               |

|         | return value register no 2.                          | CIS    | IEEE 754 float conversion register                                                                                         |

|         | temporary scratch register A                         | crl2   | multiplier control register                                                                                                |

|         | temporary scratch register B                         | cr13   | accumulator file access register                                                                                           |

|         | temporary scratch register C                         | cr14.0 | accumulator 0                                                                                                              |

|         | temporary scratch register D                         |        | accumulator 1                                                                                                              |

|         | temporary scratch register E                         |        | accumulator 2                                                                                                              |

|         | temporary scratch register F                         |        | accumulator 3                                                                                                              |

|         | general purpose register                             | cris   | MAC pipeline output                                                                                                        |

|         | general purpose register                             | cr16   | range unit control register                                                                                                |

|         | general purpose register                             | cr17   | lower limit register                                                                                                       |

|         | general purpose register                             | CLIS   | higher limit register                                                                                                      |

|         | general purpose register                             |        | MAC state save & restore entry                                                                                             |

|         | general purpose register                             | CF2U   | data I/O control register                                                                                                  |

|         | general purpose register                             | CEZI   | data I/O control register data I/O address register data I/O data input register                                           |

|         | general purpose register                             | C122   | data I/O data input register<br>image I/O control register<br>instruction store register 0<br>instruction store register 1 |

|         | general purpose register                             | 0720   | inage 1/0 control register                                                                                                 |

|         | general purpose register<br>general purpose register | 0730   | instruction store register U                                                                                               |

|         | general purpose register                             | oraz   | requences status cortain                                                                                                   |

| r28     | general purpose register                             | 6132   | sequencer scarus control register                                                                                          |

|         | general purpose register                             | 0133   | program counter                                                                                                            |

| 730     | deneral purpose register                             | Cr34   | address register interrupt table register                                                                                  |

| r31     | general purpose register                             | Cr36   | repeat count register                                                                                                      |

| r32     | general purpose register                             | CT37   | mayimum rapast count                                                                                                       |

|         | demetat bathose tedistet                             | Cr39   | maximum repeat count sequencer test register                                                                               |

|         |                                                      | cr40   | image mask control register 1                                                                                              |

| r59     | general purpose register                             |        | image mask control register 2                                                                                              |

| r60     | general purpose register                             | CT42   | window X minimum / maximum                                                                                                 |

| r61     | general purpose register                             | cr43   | window Y minimum / maximum                                                                                                 |

| I62     | general purpose register                             |        | polygon start coordinate entry                                                                                             |

|         |                                                      |        | polygon end coordinate entry                                                                                               |

| ri      | vector register (0)                                  | CT46   | polygon start/end coor register                                                                                            |

|         | vector register (1)                                  | cr47.0 | spanline start/end coor register 0                                                                                         |

| ri '    | vector register (2)                                  | cr47.1 | spanline start/end coor register 1                                                                                         |

| ri '    | vector register (3)                                  | cr47.2 | spanline start/end coor register 2                                                                                         |

|         | vector register (4)                                  | cr47.3 | spanline start/end coor register 3                                                                                         |

|         | vector register (5)                                  | cr48.0 | complex alpha mask register 0                                                                                              |

| ri ·    | vector register (6)                                  | cr48.1 | complex alpha mask register 1                                                                                              |

|         | vector register (7)                                  | cr48.2 | complex alpha mask register 2                                                                                              |

| ri ·    | vector register (8)                                  | cr48.3 | complex alpha mask register 3                                                                                              |

| ri ·    | vector register (9)                                  | cr49.0 | range clip mask register 0                                                                                                 |

| ri '    | vector register (10)                                 | cr49.1 | range clip mask register 1                                                                                                 |

| ri '    | vector register (11)                                 | cr49.2 | range clip mask register 2                                                                                                 |

|         | vector register (12)                                 | cr49.3 | range clip mask register 3                                                                                                 |

| ri '    | vector register (13)                                 | cr50.0 | transparent image mask register 0                                                                                          |

| ri v    | vector register (14)                                 | cr50.1 | transparent image mask register 1                                                                                          |

| ri      | vector register (15)                                 | cr50.2 | transparent image mask register 2                                                                                          |

| ri v    | vector register (16)                                 | cr50.3 | transparent image mask register 3                                                                                          |

|         |                                                      | cr51.0 | opaque image mask register 0                                                                                               |

|         |                                                      | cr51.1 | opaque image mask register 1                                                                                               |

| ri '    | vector register (28)                                 | cr51.2 | opaque image mask register 2                                                                                               |

| ri i    | vector register (29)                                 | cr51.3 | opaque image mask register 3                                                                                               |

| ri v    | vector register (30)                                 | 2252   | farms manager                                                                                                              |

| ri 1    | vector register (31)                                 | cr53   | bit plane mask register                                                                                                    |

|         |                                                      | 4441   | Totaground color redigiter                                                                                                 |

| dly 1   | register file delay register                         | cr55   | background color register                                                                                                  |

| -       |                                                      | cr56   | current access pointer                                                                                                     |

|         | SEQUENCER STACK                                      | cr57   | image address pointer 1 (mask ref.)                                                                                        |

|         |                                                      | cr58   | image address pointer 2                                                                                                    |

|         | top of micro stack                                   | cr59   | image address pointer 3                                                                                                    |

| stl n   | micro stack register 2                               | cr60   | display address pointer 1                                                                                                  |

| StZ h   | micro stack register 3                               | cr61   | display address pointer 2                                                                                                  |

| St3 I   | micro stack register 4                               |        |                                                                                                                            |

| St4 D   | nicro stack register 5                               | MU     | ULTIPLIER ACCUMULATOR REGISTERS                                                                                            |

| SES I   | micro stack register 5                               |        |                                                                                                                            |

| st6 n   | nicro stack register 6                               |        | C register 0 mr8 MAC register 8                                                                                            |

| st/ n   | micro stack register 7                               |        | C register 1 mr9 MAC register 9                                                                                            |

|         | DUC BROTOMANA                                        |        | C register 2 mr10 MAC register 10                                                                                          |

|         | BUS REGISTERS                                        |        | C register 3 mrll MAC register 11                                                                                          |

| Sel I B | has weet the                                         |        | C register 4 mrl2 MAC register 12                                                                                          |

|         | A bus register                                       |        | C register 5 mr13 MAC register 13                                                                                          |

|         | B bus register                                       | mr6 MA | C register 6 mrl4 MAC register 14                                                                                          |

| (       | bus register                                         | mr7 M  | C register 7 mr15 MAC register 15                                                                                          |

|         | bus register                                         | -      |                                                                                                                            |

| ,       | bus register                                         |        | C pipe.reg 0 c0 MAC coef.reg 0                                                                                             |

|         | J bus register                                       | p1 M2  | C pipe.reg 1   cl MAC coef.reg 1                                                                                           |

|         | bus register                                         | p2 MF  | C pipe.reg 2   c2 MAC coef.reg 2                                                                                           |

|         |                                                      |        |                                                                                                                            |

| Ÿ       | / bus register                                       | p3 M2  | C pipe.reg 3   c3 MAC coef.reg 3                                                                                           |

de besturingsregisters en hebben daardoor het effect van een meer dan 300-bit brede opcode.

#### Besturingsregisters

Bijna alle functie-eenheden van de Imagine zijn rijkelijk voorzien van besturingsregisters. Dat is ook onontkoombaar gezien de variëteit aan hardwareconfiguraties die bij elk van de modulen mogelijk is. Alleen via de uitgebreide instructies kan rechtstreeks aan de besturingsregisters worden gerefereerd.

In totaal bevat de chip ongeveer 250 byte aan besturingsinformatie. Een aantal daarvan wordt aangesproken als een enkel adres waarachter zich meerdere, in de regel vier, registers verschuilen die dezelfde betekenis hebben maar elk voor een verschillend segment van een datawoord. Voor de programmeur gedragen ze zich als 64 extra adressen in de driepoorts registerbank (zie tabel A).

#### Voorbeelden

In afdalende hiërarchische niveaus wordt een C-commando als:

opp = breedte \* hoogte

in assembleertaal:

mult-(opp,breedte,hoogte)

wat op het niveau van de vrije pijplijn een constructie oplevert als:

A = (breedte), B = rd(hoogte) -: F = mult(A,B,iss) -: wr(opp,F)

In de praktijk zal de parallelliteit in veel opdrachten verder gaan dan deze vier gelijktijdige instructies. Een voorbeeld daarvan is het volgende onderdeel uit een algoritme voor het roteren en interpoleren van een kleurenbeeld:

B = rd2×16(ri) -: Q = shift(B,A) -: F = add(Q,U) -: DA = rdAd(F) -: D = word(ul), V = input -: M = macb(D,V)

Deze herbergt in totaal 38 instructies:

- 2×16-bit register lezen

- 2×16-bit registeradres ophogen

- 1×10-bit constante lezen

- 2×16-bit woord schuiven

- 2×16-bit constante lezen

- 2×16-bit waarde optellen

- 4x8-bit 2D-geheugendata uitlezen

- 4x8-bit beeldgeheugendata uitlezen

- 1x32-bit beeldgeheugenadres ophogen

- 4x8-bit waarde vermenigvuldigen

- 4×12-bit accumulatorregister lezen

- 4×12-bit waarde accumuleren

- 4×12-bit accumulatorregister schrijven

- 2×5-bit registeradres accumulator ophogen

Tabel A. De besturingsregisters zijn programmeertechnisch te zien als adresblok boven de registerbank.

het feitelijk weer te geven beeld ontstaat. Die twee zijn identiek in die zin dat ze beide maximaal 128 beeldpunten kunnen bevatten in een matrix van 4x32. Waar het transparante patroon per pixel al of niet veranderingen toestaat, kent zijn dekkende tegenhanger per beeldpunt een definitieve voor- of achtergrondkleur toe.

#### Instructieverwerking

Programmeurs hebben vier typen instructies tot hun beschikking om de loop van het programma te beïnvloeden: lus-, aanroepen terugkeeropdrachten en een tiental voorwaardelijke sprongen. Waar deze naar verwijzen hangt af van de adresseringsvorm, die eveneens in de opcode is opgenomen. Er zijn zeven mogelijkheden, variërend van een rechtstreekse locatie of offset tot een indirect adres via stack of register.

De programmabesturingseenheid heeft de beschikking over een kleine, snelle stack op de chip die kan worden gebruikt voor diverse doeleinden. Een voor de hand liggende toepassing is de opslag van verwerVoorbeeld van een venstergeoriënteerde schakeringsoperatie met programma en registerinstellingen.

kingstoestand en terugkeeradres bij een interrupt, die genoeg heeft aan vijf cyclussen oftewel krap 85 ns. Meervoudige interrupts – van belang bij multimediatoepassingen – laten zich eveneens programmeren en zijn in 1 à 2 µs af te handelen. Verder is de stack beschikbaar voor het schrijven van kleine, snelle procedures in assembleertaal die niet de gebruikelijke subroutine-overhead hebben.

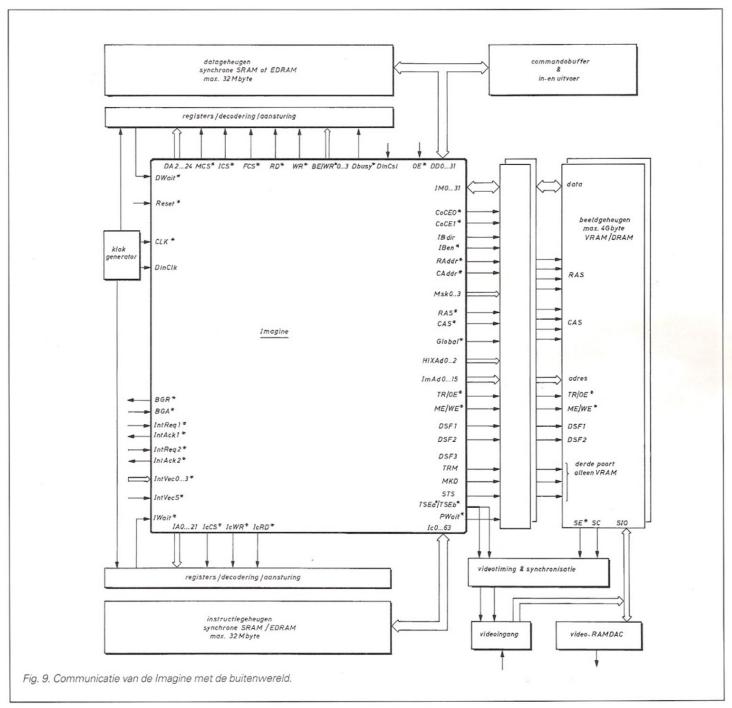

#### Invoer en uitvoer

Drie eenheden verzorgen de communicatie met de buitenwereld (fig. 9). Een daarvan is ingericht voor de gegevensuitwisseling met het conventionele geheugen en met in- en uitvoerapparatuur. Hierbij transporteert een 32-bit datakanaal de informatie van en naar de chip terwijl de 23-bit adresbus (A2..A24) het te adresseren gebied op 8 Mwoord ofwel 32 Mbyte brengt. Vier schrijfsignalen zorgen ervoor dat elk woord op byteniveau kan worden gewijzigd. Bij het lezen komt altijd het hele 32-bit woord binnen, waarna de in- en uitvoereenheid aan de hand van de bits A0 en A1 er, indien noodzakelijk, de gewenste 8- of 16-bit sectie uit moet lichten. Behalve de gebruikelijke dataoverdracht zijn ook tweeen driedimensionale geheugentoegangen mogelijk, wat het werken met beelden, volume-objecten, conversietabellen en deraeliike ondersteunt.

De instructiestroom heeft zijn eigen externe kanalen en een gescheiden geheugenblok. Maximaal 32 Mbyte kan het programmageheugen groot zijn, bij een indeling van 4Mx64 bit. Het binnenhalen van de opdrachten vindt plaats onder beheer van de programmabesturingseenheid en verloopt tamelijk recht-toe-recht-aan. Met een 22-bit adres wordt steeds een volgend instructiewoord aangewezen, dat vervolgens via een afzonderlijke 64-bit bus wordt binnengehaald.

#### Beeldgeheugen

De derde gegevensstroom heeft betrekking op de opslag, het wijzigen en het terughalen van beelden. In alle gevallen gebeurt dit in de vorm van een tweedimensionale matrix van beeldpunten. De pixels zelf kunnen echter een variëteit aan formaten en indelingen hebben, van 8-bit grijs of pseudokleur via 16-bit monochroom tot 32-bit kleur of diepte. Vooral bij de 32-bit beeldpunten zijn diverse kleurenrepresentaties mogelijk, zoals RGB, CMYK, YUV en HSL.

Al deze formaten hebben geen invloed op de wijze van opslag en maar in zeer beperkte >

mate op de verwerking van de data. Alle gegevensblokken van en naar het beeldgeheugen worden gezien als vectoren met een lengte van 1 tot 32 woorden, waarbij elk woord 1 tot 4 pixels bevat. Vectoren vertegenwoordigen horizontale stroken van het plaatje en lopen van links naar rechts, overeenkomstig met wat in de meeste applicaties gebruikelijk is. Daarbij zorgt de beeldgeheugenaansturing voor het genereren van het adres aan de hand van de X/Y-positie, zodat elk willekeurig beeldsegment kan worden aangesproken aan de hand van zijn locatie binnen de afbeelding.

Behalve voor pixels is het beeldgeheugen ook geschikt voor het herbergen van andere datastructuren. Te denken valt aan lijsten en databanken met grafische elementen. Ook andere Windows- en CAD-gerelateerde informatie kan hierin worden opgeslagen.

Het geheugen zelf kan zowel zijn opgebouwd uit conventionele dynamische RAM's als uit de veel duurdere maar efficiëntere twee- en driepoorts video-RAM's. Daarbij kan de 66-MHz versie van de Imagine goed uit de voeten met een toegangstijd van 70 ns.

De interface naar het beeldgeheugen kan geheel softwarematig worden bestuurd. In de meeste gevallen zal dat niet verder gaan dan normale lees- en schrijfacties. De commando's die bijvoorbeeld het regelen van de verversingscyclus, het synchroniseren van horizontale of verticale sync-pulsen met perifere apparatuur of het gelijktijdig aansturen van verschillende videosystemen mogelijk maken, zullen alleen in speciale gevallen nodig zijn.

Inl.: Arcobel Graphics, postbus 1323, 5203 DM Den Bosch, tel.: (073) 444144, fax: (073) 444150.

### Hans de Vries

Co-founder and Technical Director of Arcobel Graphics BV.

Architect ot the Imagine Graphics and Image processor

www.chip-architect.com www.physics-quest.org